বিভিন্ন ধরনের লজিক ফ্যামিলি পাওয়া যায় যেগুলো ডিজিটাল লজিক সার্কিট ডিজাইন করতে ব্যবহৃত হয়; রেজিস্টর ট্রানজিস্টর লজিক (RTL), ইমিটার কাপলড লজিক (ECL), ডায়োড ট্রানজিস্টর লজিক (DTL), কমপ্লিমেন্টারি মেটাল অক্সাইড সেমিকন্ডাক্টর লজিক (CMOS), এবং ট্রানজিস্টর-ট্রানজিস্টর লজিক (TTL) . এই লজিক পরিবারগুলির মধ্যে, DTL লজিক পরিবার সাধারণত 1960 এবং 1970 এর আগে আরও উন্নত লজিক পরিবারগুলিকে প্রতিস্থাপন করতে ব্যবহৃত হত CMOS এবং TTL। ডায়োড-ট্রানজিস্টর লজিক একটি শ্রেণী ডিজিটাল সার্কিট যেটি ডায়োড এবং ট্রানজিস্টর দিয়ে ডিজাইন করা হয়েছে। তাই ডায়োড এবং ট্রানজিস্টরের সংমিশ্রণটি বেশ ছোট উপাদানগুলির সাথে জটিল লজিক ফাংশন তৈরি করার অনুমতি দেয়। এই নিবন্ধে সংক্ষিপ্ত তথ্য প্রদান করে DTL বা ডায়োড ট্রানজিস্টর লজিক এবং এর অ্যাপ্লিকেশন।

ডায়োড ট্রানজিস্টর লজিক কি?

ডায়োড ট্রানজিস্টর লজিক হল একটি লজিক সার্কিট যা ডিজিটাল লজিক পরিবারের অন্তর্গত যা ডিজিটাল সার্কিট তৈরি করতে ব্যবহৃত হয়। এই সার্কিট দিয়ে ডিজাইন করা যেতে পারে ডায়োড এবং ট্রানজিস্টর যেখানে ইনপুট সাইডে ডায়োড ব্যবহার করা হয় এবং আউটপুট সাইডে ট্রানজিস্টর ব্যবহার করা হয়, তাই এটি DTL নামে পরিচিত। DTL হল একটি নির্দিষ্ট শ্রেণীর সার্কিট যা বর্তমান ডিজিটাল ইলেকট্রনিক্সে বৈদ্যুতিক সংকেত প্রক্রিয়াকরণের জন্য ব্যবহৃত হয়।

এই লজিক সার্কিটে, ডায়োডগুলি লজিক ফাংশন সঞ্চালনে উপযোগী, যখন ট্রানজিস্টরগুলি পরিবর্ধন ফাংশনগুলি সম্পাদন করতে ব্যবহৃত হয়। তুলনায় DTL অনেক সুবিধা আছে প্রতিরোধক ট্রানজিস্টার যুক্তি মত; উচ্চ ফ্যান-আউট মান এবং উচ্চ শব্দ মার্জিন এইভাবে, DTL RTL পরিবার প্রতিস্থাপিত হয়। দ্য ডায়োড ট্রানজিস্টর লজিকের বৈশিষ্ট্য প্রধানত অন্তর্ভুক্ত; ডিজিটাল সংস্কৃতিহীন, ডিজিটাল কৌশলবিদ, ডিজিটাল আর্কিটেক্ট, সাংগঠনিক চৌকস, গ্রাহক কেন্দ্রবিদ, ডেটা অ্যাডভোকেট, ডিজিটাল কর্মক্ষেত্রের ল্যান্ডস্কেপার এবং ব্যবসায়িক প্রক্রিয়া অপ্টিমাইজার।

ডায়োড ট্রানজিস্টর লজিক সার্কিট

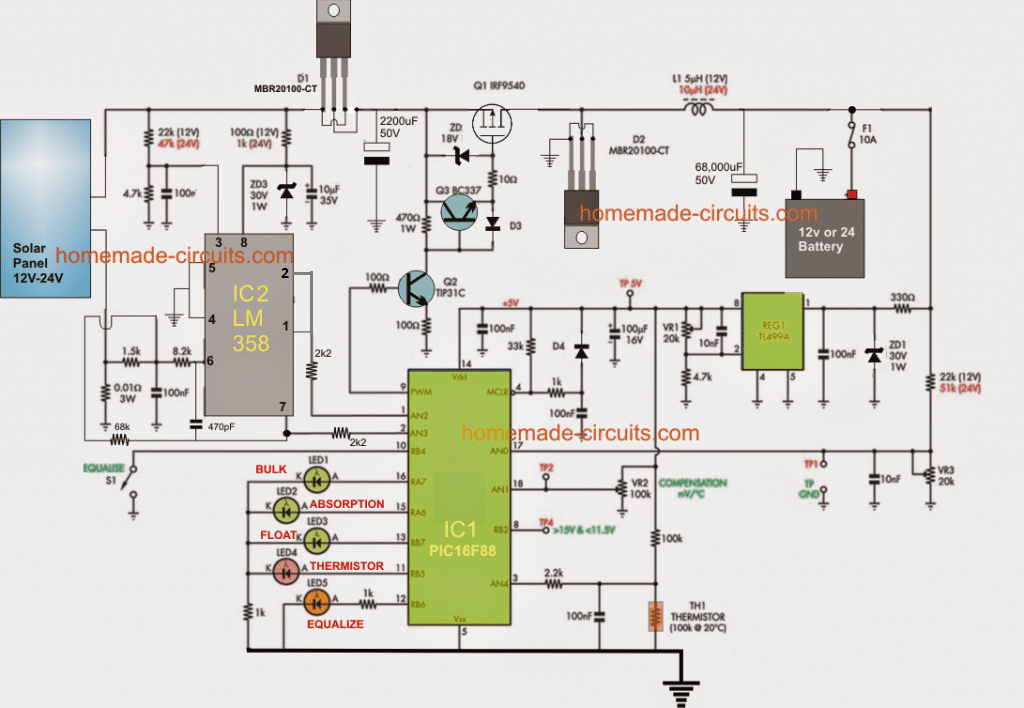

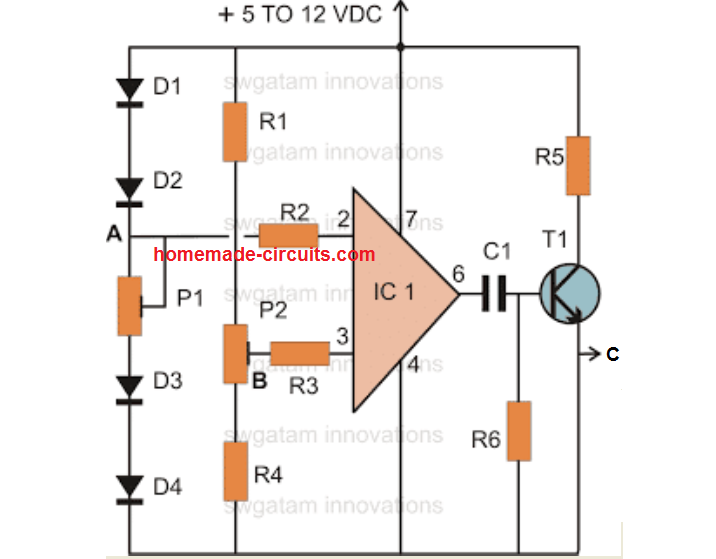

ডায়োড ট্রানজিস্টর লজিক সার্কিট নীচে দেখানো হয়েছে। এটি একটি দুই-ইনপুট ডায়োড ট্রানজিস্টর লজিক NAND গেট সার্কিট। এই সার্কিটটি দুটি ডায়োড এবং একটি ট্রানজিস্টর দিয়ে ডিজাইন করা হয়েছে যেখানে দুটি ডায়োডকে D1 এবং D2 দিয়ে নির্দেশ করা হয়েছে এবং রোধকে R1 দিয়ে নির্দেশ করা হয়েছে যা লজিক সার্কিটের ইনপুট সাইড তৈরি করে। Q1 ট্রানজিস্টর CE কনফিগারেশন এবং R2 রোধ আউটপুট সাইড গঠন করে। এই সার্কিটের 'C1' ক্যাপাসিটরটি সুইচিংয়ের পুরো সময় জুড়ে একটি ওভারড্রাইভ কারেন্ট দিতে ব্যবহৃত হয় এবং এটি সুইচিং সময়কে কিছু স্তরে হ্রাস করে।

ডায়োড ট্রানজিস্টর লজিক ওয়ার্কিং

যখনই A & B সার্কিটের উভয় ইনপুট কম থাকে, তখন D1 এবং D2 উভয় ডায়োডই ফরোয়ার্ড বায়াসড হয়ে যাবে, এইভাবে এই ডায়োডগুলি সামনের দিকের মধ্যে পরিচালনা করবে। এইভাবে ভোল্টেজ সরবরাহের কারণে বর্তমান সরবরাহ (+VCC = 5V) R1 প্রতিরোধক এবং দুটি ডায়োড জুড়ে GND-কে সরবরাহ করবে। R1 প্রতিরোধকের মধ্যে ভোল্টেজ সরবরাহ কমে যায় এবং Q1 ট্রানজিস্টর চালু করার জন্য এটি যথেষ্ট হবে না, এইভাবে Q1 ট্রানজিস্টর কাট-অফ মোডে থাকবে। সুতরাং, 'Y' টার্মিনালে o/p হবে লজিক 1 বা উচ্চ মান।

যখন ইনপুটগুলির যেকোনো একটি কম হয়, তখন সংশ্লিষ্ট ডায়োডটি ফরোয়ার্ড-বায়াসড হবে, তাই একটি অনুরূপ অপারেশন ঘটবে। যেহেতু এই ডায়োডগুলির যেকোনো একটি ফরোয়ার্ড বায়াসড, তাহলে পুরো ফরোয়ার্ড-বায়াসড ডায়োড জুড়ে গ্রাউন্ডে কারেন্ট সরবরাহ করা হবে, এইভাবে 'Q1' ট্রানজিস্টর কাট-অফ মোডের মধ্যে থাকবে, তাই 'Y' টার্মিনালে আউটপুট হবে উচ্চ বা যুক্তি 1.

যখনই উভয় A এবং B ইনপুট উচ্চ হবে তখন উভয় ডায়োড বিপরীত পক্ষপাতী হবে, এইভাবে উভয় ডায়োড পরিচালনা করবে না। সুতরাং এই অবস্থায়, Q1 ট্রানজিস্টরকে পরিবাহী মোডে চালিত করার জন্য +VCC সরবরাহ থেকে ভোল্টেজ যথেষ্ট হবে।

তাই ট্রানজিস্টর ইমিটার এবং কালেক্টর টার্মিনাল জুড়ে সঞ্চালন করে। 'R2' রোধের মধ্যে পুরো ভোল্টেজ কমে যায় এবং 'Y' টার্মিনালে আউটপুট কম o/p থাকবে এবং কম বা লজিক 0 হিসাবে বিবেচিত হবে।

সঠিক তালিকা

DTL সত্য সারণী নীচে দেখানো হয়েছে.

|

ক |

খ | এবং |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

ডায়োড ট্রানজিস্টর লজিক প্রচারের বিলম্ব বেশ বড়। যখনই সমস্ত ইনপুট যুক্তিযুক্ত হয় তখন ট্রানজিস্টরটি বেস অঞ্চলের মধ্যে স্যাচুরেশন এবং চার্জ বিল্ড আপে চলে যায়। যখনই একটি ইনপুট কম হয় তখন এই চার্জটি সরিয়ে ফেলা উচিত, প্রচারের সময় পরিবর্তন করে। ডায়োড ট্রানজিস্টর লজিককে এক উপায়ে গতি বাড়ানোর কৌশল হল রোধ R3 জুড়ে একটি ক্যাপাসিটর যুক্ত করা। এখানে, এই ক্যাপাসিটর বেস টার্মিনালে জমে থাকা চার্জ বাদ দিয়ে ট্রানজিস্টর বন্ধ করতে সহায়তা করে। এই সার্কিটের ক্যাপাসিটরটি প্রথম বেস ড্রাইভকে উন্নত করার মাধ্যমে ট্রানজিস্টর চালু করতেও সহায়তা করে।

সংশোধিত ডায়োড ট্রানজিস্টর লজিক

পরিবর্তিত DTL NAND গেট নীচে দেখানো হয়েছে। প্রতিরোধক এবং ক্যাপাসিটর উপাদানগুলির বড় মানগুলি একটি আইসিতে অর্থনৈতিকভাবে তৈরি করা খুব কঠিন। তাই নিম্নোক্ত DTL NAND গেট সার্কিটটি শুধুমাত্র C1 ক্যাপাসিটর বাদ দিয়ে, রোধের মান হ্রাস করে এবং ব্যবহার করে IC বাস্তবায়নের জন্য পরিবর্তন করা যেতে পারে ট্রানজিস্টর এবং ডায়োড যেখানেই সম্ভব। এই পরিবর্তিত সার্কিটটি কেবল একটি একক পজিটিভ সাপ্লাই ব্যবহার করে এবং এই সার্কিটে D1 এবং D2 ডায়োড সহ একটি ইনপুট স্টেজ, একটি R3 প্রতিরোধক এবং একটি AND গেট রয়েছে যা একটি ট্রানজিস্টরাইজড ইনভার্টারের মাধ্যমে অনুসরণ করা হয়।

কাজ করছে

এই সার্কিটের কাজ হল, এই সার্কিটে দুটি ইনপুট টার্মিনাল A এবং B আছে এবং A & B এর মত ইনপুট ভোল্টেজগুলি উচ্চ বা নিম্ন হতে পারে।

যদি উভয় ইনপুট A & B কম হয় বা লজিক 0 হয়, তাহলে উভয় ডায়োডই এগিয়ে যাবে পক্ষপাতদুষ্ট, এইভাবে 'M' এ সম্ভাব্য হল একটি ডায়োডের ভোল্টেজ ড্রপ যা 0.7 V। যদিও 'Q' ট্রানজিস্টরকে পরিবাহীতে চালিত করতে , তারপর 'Q' ট্রানজিস্টরের ডায়োড D3, D4 এবং BE জংশনকে ফরোয়ার্ড করার জন্য আমাদের 2.1 V প্রয়োজন, এইভাবে এই ট্রানজিস্টরটি কাটঅফ এবং Y = 1 আউটপুট প্রদান করে।

Y = Vcc = যুক্তি 1 এবং A = B = 0 এর জন্য, Y = 1 বা উচ্চ।

যদি ইনপুটগুলির মধ্যে যেকোন একটি A বা B কম হয়, তাহলে ইনপুটগুলির মধ্যে যেকোনো একটিকে +Vcc-এর সাথে সংযুক্ত যেকোনো টার্মিনালের সাথে GND-এর সাথে সংযুক্ত করা যেতে পারে, সমতুল্য ডায়োড পরিচালনা করবে এবং VM ≅ 0.7 V & Q ট্রানজিস্টর কেটে যাবে। , এবং আউটপুট 'Y' = 1 বা যুক্তি উচ্চ প্রদান করুন।

যদি A = 0 এবং B =1 (বা) যদি A = 1 এবং B = 0 হয়, তাহলে Y = 1 বা HIGH আউটপুট।

যদি দুটি ইনপুট যেমন A এবং B উভয়ই উচ্চ হয় এবং A এবং B উভয়ই সহজভাবে + Vcc এর সাথে সংযুক্ত থাকে, তাহলে উভয় D1 এবং D2 ডায়োড বিপরীত-ভিত্তিক হবে এবং তারা পরিচালনা করে না। D3 এবং D4 ডায়োডগুলি সামনের দিকে পক্ষপাতমূলক এবং বেস টার্মিনালে কারেন্ট কেবল Rd, D3, এবং D4 এর মাধ্যমে Q ট্রানজিস্টরে সরবরাহ করা হয়। ট্রানজিস্টরটিকে স্যাচুরেশনে চালিত করা যেতে পারে এবং o/p ভোল্টেজ একটি কম ভোল্টেজ হবে।

A = B = 1 এর জন্য, আউটপুট Y = 0 বা LOW।

সংশোধিত DTL-এর অ্যাপ্লিকেশনগুলির মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

বৃহত্তর ফ্যান আউট সম্ভব পরবর্তী গেট যুক্তি উচ্চ অবস্থার সঙ্গে উচ্চ প্রতিবন্ধকতা থাকার কারণে. এই সার্কিট উচ্চতর শব্দ প্রতিরোধ ক্ষমতা আছে. প্রতিরোধক এবং ক্যাপাসিটরের পরিবর্তে একাধিক ডায়োডের ব্যবহার এই সার্কিটটিকে ইন্টিগ্রেটেড সার্কিট ফর্মের মধ্যে খুব অর্থনৈতিক করে তুলবে।

ডায়োড ট্রানজিস্টর লজিক নর গেট

ডায়োড ট্রানজিস্টর লজিক NOR গেটটি ডিআরএল বা ট্রানজিস্টর ইনভার্টার সহ গেট সহ DTL NAND গেটের অনুরূপভাবে ডিজাইন করা হয়েছে। একটি সাধারণ আউটপুটের মাধ্যমে বিভিন্ন DTL ইনভার্টারগুলিকে একত্রিত করে DTL NOR সার্কিটগুলিকে আরও মার্জিতভাবে ডিজাইন করা যেতে পারে। এই পদ্ধতিতে, NOR গেটের জন্য প্রয়োজনীয় ইনপুট দেওয়ার জন্য বেশ কয়েকটি ইনভার্টার একত্রিত হতে পারে।

এই সার্কিটটি ডিটিএল ইনভার্টার সার্কিটের উপাদানগুলি ছাড়াও ডিজাইন করা যেতে পারে পাওয়ার সাপ্লাই এবং দুই 4.7 কে প্রতিরোধক , 1N914 বা 1N4148 সিলিকন ডায়োড। নীচে দেখানো সার্কিট অনুযায়ী সার্কিট সংযোগ করুন।

কাজ করছে

সংযোগ করা হয়ে গেলে, সার্কিটে পাওয়ার সাপ্লাই প্রদান করতে হবে। এর পরে, একটি ডিপ সুইচ দিয়ে পাওয়ার সাপ্লাই থেকে A & B এ চারটি সম্ভাব্য ইনপুট সমন্বয় প্রয়োগ করুন। এখন প্রতিটি ইনপুট সংমিশ্রণের জন্য, আউটপুট 'Q' এর লজিক অবস্থাটি নোট করতে হবে এলইডি এবং সেই আউটপুট রেকর্ড করুন। NOR গেট অপারেশনের সাথে ফলাফলের তুলনা করুন। একবার আপনি আপনার পর্যবেক্ষণ শেষ করে, তারপর পাওয়ার সাপ্লাই বন্ধ করুন।

|

ক |

খ |

Y = (A+B)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

ডায়োড ট্রানজিস্টর লজিক এবং গেট

ডায়োড ট্রানজিস্টর লজিক এবং গেট নীচে দেখানো হয়েছে। এই বর্তনীতে, যুক্তির মত রাজ্যগুলি; 1 এবং 0 কে +5V পজিটিভ লজিক এবং 0V অনুরূপভাবে নেওয়া হয়।

যখনই A1, A2 (বা) A3 থেকে কোনো ইনপুট কম লজিক অবস্থায় থাকে তখন সেই ইনপুটটির সাথে সংযুক্ত ডায়োডটি ফরওয়ার্ড বায়াসে থাকবে তারপরে, ট্রানজিস্টর কেটে যাবে এবং আউটপুট হবে LOW বা লজিক 0 একইভাবে, যদি তিনটি ইনপুটই লজিক 1 এ থাকে তাহলে ডায়োড কন্ডাক্ট এবং ট্রানজিস্টরের কোনোটিই ভারীভাবে সঞ্চালিত হয় না। এর পরে, ট্রানজিস্টরটি স্যাচুরেট হয় এবং আউটপুট হাই বা লজিক 1 হবে।

ডায়োড ট্রানজিস্টর লজিক এবং গেটের সত্য সারণী নীচে দেখানো হয়েছে।

|

A1 |

A2 | A3 |

Y = A.B |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

DTL, TTL এবং RTL এর মধ্যে তুলনা

DTL, TTL, এবং RTL এর মধ্যে পার্থক্যগুলি নীচে আলোচনা করা হয়েছে।

| ডিটিএল | টিটিএল |

আরটিএল |

| ডিটিএল শব্দটি ডায়োড-ট্রানজিস্টর লজিকের জন্য দাঁড়িয়েছে। | TTL শব্দটি ট্রানজিস্টর-ট্রানজিস্টর লজিকের জন্য দাঁড়িয়েছে। | আরটিএল শব্দটি রেসিস্টর-ট্রানজিস্টর লজিকের জন্য দাঁড়িয়েছে। |

| DTL-এ, লজিক গেটগুলি PN জংশন ডায়োড এবং ট্রানজিস্টর দিয়ে ডিজাইন করা হয়েছে। | একটি TTL-এ, লজিক গেটগুলি BJTs দিয়ে ডিজাইন করা হয়েছে।

|

আরটিএল-এ, লজিক গেটগুলি প্রতিরোধক এবং ট্রানজিস্টর দিয়ে ডিজাইন করা হয়েছে। |

| ডিটিএল-এ, ডায়োডগুলি i/p উপাদান হিসাবে ব্যবহৃত হয় এবং ট্রানজিস্টরগুলি o/p উপাদান হিসাবে ব্যবহৃত হয়। | টিটিএল-এ, একটি ট্রানজিস্টর প্রশস্তকরণের জন্য ব্যবহৃত হয় যেখানে অন্য ট্রানজিস্টর সুইচিংয়ের উদ্দেশ্যে ব্যবহার করা হয়। | RTL-এ রোধ i/p কম্পোনেন্ট হিসেবে এবং ট্রানজিস্টর ব্যবহার করা হয় o/p কম্পোনেন্ট হিসেবে |

| DTL প্রতিক্রিয়া RTL এর তুলনায় ভাল। | TTL প্রতিক্রিয়া DTL এবং RTL এর থেকে অনেক ভালো। | RTL প্রতিক্রিয়া ধীর। |

| পাওয়ার লস কম। | এটির পাওয়ার লস খুবই কম। | পাওয়ার লস বেশি। |

| এর নির্মাণ জটিল। | এর নির্মাণ খুবই সহজ। | এর নির্মাণ সহজ। |

| DTL ন্যূনতম ফ্যানআউট 8। | টিটিএল ন্যূনতম ফ্যানআউট 10। | RTL ন্যূনতম ফ্যানআউট 5। |

| প্রতিটি গেটের জন্য শক্তি অপচয় সাধারণত 8 থেকে 12 মেগাওয়াট হয়। | প্রতিটি গেটের জন্য শক্তি অপচয় সাধারণত 12 থেকে 22 মেগাওয়াট হয়। | প্রতিটি গেটের জন্য শক্তি অপচয় সাধারণত 12 মেগাওয়াট হয়। |

| এর শব্দ প্রতিরোধ ক্ষমতা ভালো। | এর শব্দ প্রতিরোধ ক্ষমতা খুব ভালো। | এর শব্দ প্রতিরোধ ক্ষমতা মাঝারি। |

| গেটের জন্য এটির সাধারণ প্রচার বিলম্ব 30 এনএস। | গেটের জন্য এর সাধারণ প্রচার বিলম্ব হল 12 থেকে 6 এনএস। | গেটের জন্য এটির সাধারণ প্রচার বিলম্ব হল 12 এনএস। |

| এর ঘড়ির হার 12 থেকে 30 MHZ। | এর ঘড়ির হার 15 থেকে 60 MHZ। | এর ক্লক রেট 8 MHZ। |

| এটি ফাংশন একটি মোটামুটি উচ্চ সংখ্যা আছে. | এটা ফাংশন একটি খুব উচ্চ সংখ্যা আছে. | এটা ফাংশন একটি উচ্চ সংখ্যা আছে. |

| DTL লজিক বেসিক সুইচিং এবং ডিজিটাল সার্কিটে ব্যবহার করা হয়। | TTL লজিক আধুনিক ডিজিটাল সার্কিট এবং ইন্টিগ্রেটেড সার্কিটে ব্যবহৃত হয়। | RTL পুরানো কম্পিউটারের মধ্যে ব্যবহৃত হয়। |

সুবিধাদি

একটি ডায়োড ট্রানজিস্টর লজিক সার্কিটের সুবিধাগুলির মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

- RTL-এর তুলনায় DTL-এর সুইচিং গতি দ্রুততর।

- DTL সার্কিটের মধ্যে ডায়োডের ব্যবহার এগুলিকে সস্তা করে তোলে কারণ ICs-এ ডায়োড তৈরি করা প্রতিরোধক এবং ক্যাপাসিটরের তুলনায় সহজ।

- DTL সার্কিটের মধ্যে পাওয়ার লস খুবই কম।

- DTL সার্কিটগুলির দ্রুত স্যুইচিং গতি রয়েছে।

- DTL এর ফ্যান-আউট এবং উন্নত নয়েজ মার্জিন রয়েছে।

দ্য ডায়োড ট্রানজিস্টর লজিক সার্কিটের অসুবিধা নিম্নলিখিত অন্তর্ভুক্ত.

- TTL-এর তুলনায় DTL-এর অপারেটিং গতি কম।

- এটি একটি অত্যন্ত বড় গেট প্রচার বিলম্ব আছে.

- উচ্চ ইনপুটের জন্য, DTL এর আউটপুট স্যাচুরেশনে যায়।

- এটি পুরো অপারেশন জুড়ে তাপ উৎপন্ন করে।

অ্যাপ্লিকেশন

দ্য ডায়োড ট্রানজিস্টর লজিকের অ্যাপ্লিকেশন নিম্নলিখিত অন্তর্ভুক্ত.

- ডায়োড- ট্রানজিস্টর লজিক যেখানে ডিজিটাল সার্কিট ডিজাইন ও ফেব্রিকেট করতে ব্যবহৃত হয় যুক্তির পথ ইনপুট পর্যায়ে ডায়োড এবং আউটপুট পর্যায়ে BJT ব্যবহার করুন।

- DTL হল একটি নির্দিষ্ট ধরনের সার্কিট যা বর্তমান ডিজিটাল ইলেকট্রনিক্সে বৈদ্যুতিক সংকেত প্রক্রিয়াকরণের জন্য ব্যবহৃত হয়।

- সহজ লজিক সার্কিট তৈরি করতে DTL ব্যবহার করা হয়।

এইভাবে, এই ডায়োড ট্রানজিস্টর লজিকের একটি ওভারভিউ , সার্কিট, কাজ, সুবিধা, অসুবিধা, এবং অ্যাপ্লিকেশন. RTL সার্কিটগুলির তুলনায় DTL সার্কিটগুলি আরও জটিল, কিন্তু এই যুক্তিটি RTL এর উচ্চতর ফ্যান আউট ক্ষমতা এবং উন্নত নয়েজ মার্জিনের কারণে পরিবর্তন করেছে কিন্তু DTL-এর গতি ধীর। এখানে আপনার জন্য একটি প্রশ্ন, আরটিএল কি?