ইলেকট্রনিক্সের ডোমেনে, প্রতিটি উপাদান যে সর্বাধিক গুরুত্বপূর্ণ ধারণাটি কাজ করে তা হ'ল ' যুক্তির পথ “। যেমন যুক্তি গেটগুলির ধারণাটি প্রতিটি কার্যকারিতায় যেমন ইন্টিগ্রেটেড সার্কিট, সেন্সর, স্যুইচিংয়ের উদ্দেশ্য, মাইক্রোকন্ট্রোলার এবং প্রসেসর, এনক্রিপশন এবং ডিক্রিপশন উদ্দেশ্যে এবং অন্যান্যতে প্রয়োগ করা হয়। এগুলি ছাড়াও লজিক গেটসের বিস্তৃত অ্যাপ্লিকেশন রয়েছে। অ্যাডার, সাবট্রেক্টর, ফুলের মতো অনেক ধরণের লজিক গেট রয়েছে সংযোজন , পূর্ণ বিয়োগকারী, অর্ধ বিয়োগকারী এবং আরও অনেক। সুতরাং, এই নিবন্ধটি সম্মিলিত তথ্য সরবরাহ করে অর্ধ বিয়োগকারক সার্কিট , অর্ধ বিয়োগকার সত্যের টেবিল , এবং সম্পর্কিত ধারণা।

অর্ধ বিয়োগকারক কী?

অর্ধ বিয়োগকারকে নিয়ে আলোচনা করার আগে আমাদের বাইনারি বিয়োগফল জানতে হবে। বাইনারি বিয়োগফলে, বিয়োগের প্রক্রিয়াটি গণিত বিয়োগের মতো to গাণিতিক বিয়োগফলে বেস 2 নম্বর সিস্টেমটি ব্যবহৃত হয় যেখানে বাইনারি বিয়োগফলে বাইনারি সংখ্যাগুলি বিয়োগের জন্য ব্যবহৃত হয়। ফলস্বরূপ পদগুলি পার্থক্য এবং withণের সাথে বোঝানো যেতে পারে।

অর্ধ বিয়োগকারক সর্বাধিক প্রয়োজনীয় সংযুক্ত যুক্তিযুক্ত সার্কিট যা ব্যবহৃত হয় ডিজিটাল ইলেকট্রনিক্স । মূলত, এটি একটি বৈদ্যুতিন ডিভাইস বা অন্য কথায়, আমরা এটি লজিক সার্কিট হিসাবে বলতে পারি। এই সার্কিটটি দুটি বাইনারি অঙ্কের বিয়োগফল করতে ব্যবহৃত হয়। পূর্ববর্তী নিবন্ধে, আমরা ইতিমধ্যে আলোচনা করেছি অর্ধ সংযোজক এবং একটি পূর্ণ অ্যাডারের সার্কিটের ধারণা যা গণনার জন্য বাইনারি সংখ্যা ব্যবহার করে। একইভাবে, বিয়োগফলের সার্কিট বিয়োগের জন্য বাইনারি সংখ্যা (0,1) ব্যবহার করে। অর্ধ বিয়োগকারের সার্কিট দুটি দিয়ে তৈরি করা যেতে পারে ল্যান্ডিক গেটগুলি যথা ন্যানড এবং এক্স-ওআর গেটস । এই সার্কিটটি পার্থক্যের পাশাপাশি দুটি elementsণ গ্রহণের মতো দুটি উপাদান দেয়।

বাইনারি বিয়োগের মতো, প্রধান অঙ্ক 1, আমরা orrowণ উত্পন্ন করতে পারি যখন সাবট্রেন্ড 1টি 0 মিনিটের চেয়ে উচ্চতর এবং এর কারণে orrowণ গ্রহণের প্রয়োজন হবে। নিম্নলিখিত উদাহরণটি দুটি বাইনারি বিটের বাইনারি বিয়োগফল দেয়।

প্রথম সংখ্যা | দ্বিতীয় সংখ্যা | পার্থক্য | ধার |

0 | 0 | 0 | 0 |

ঘ | 0 | ঘ | 0 |

| 0 | ঘ | ঘ | ঘ |

| ঘ | ঘ | 0 | 0 |

উপরের বিয়োগফলে, দুটি অঙ্ককে এ এবং বি দ্বারা প্রতিনিধিত্ব করা যেতে পারে এই দুটি অঙ্কটি বিয়োগ করা যেতে পারে এবং ফলস্বরূপ বিটগুলি পার্থক্য এবং orrowণ হিসাবে প্রদান করে।

যখন আমরা প্রথম দুটি এবং চতুর্থ সারিগুলি পর্যবেক্ষণ করি তখন এই সারিগুলির মধ্যে পার্থক্য হয়, তারপরে পার্থক্য এবং orrowণ সমান হয় কারণ সাবট্রেন্ডটি মিনিটের তুলনায় কম থাকে। একইভাবে, আমরা যখন তৃতীয় সারিটি লক্ষ্য করি, তখন মানফলটি সাবট্রেন্ড থেকে বিয়োগ করা হয়। সুতরাং পার্থক্য এবং orrowণ বিট 1 হয় কারণ subtrahend ডিজিটটি minuend অঙ্কের চেয়ে উচ্চতর।

এই সংযুক্ত সার্কিট যে কোনও ধরণের জন্য একটি প্রয়োজনীয় সরঞ্জাম ডিজিটাল সার্কিট ইনপুট এবং আউটপুটগুলির সম্ভাব্য সমন্বয়গুলি জানতে। উদাহরণস্বরূপ, যদি বিয়োগকারের দুটি ইনপুট থাকে তবে ফলস্বরূপ ফলাফলগুলি চারটি হবে। অর্ধ বিয়োগকারকের ও / পি নীচের সারণীতে উল্লেখ করা হয়েছে যা পার্থক্য বিটকে পাশাপাশি bণ গ্রহণের বিটকেও নির্দেশ করবে। সার্কিটের সত্যের টেবিলের ব্যাখ্যাটি লজিক গেটের মতো EX-OR লজিক গেট এবং অ্যান্ড গেট অপারেশন এর পরে নট গেট ব্যবহার করে করা যেতে পারে।

সত্যের টেবিলটি ব্যবহার করে সমাধান করা কে-ম্যাপ নীচে প্রদর্শিত হয়।

অর্ধ বিয়োগকার কে মানচিত্র

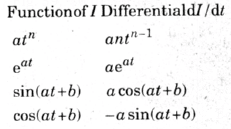

দ্য অর্ধ বিয়োগকার এক্সপ্রেশন সত্য টেবিল এবং কে-ম্যাপ ব্যবহার করে হিসাবে প্রাপ্ত করা যেতে পারে

পার্থক্য (ডি) = ( x'y + xy ')

= x ⊕ y

ধার (খ) = x'y

লজিক্যাল সার্কিট

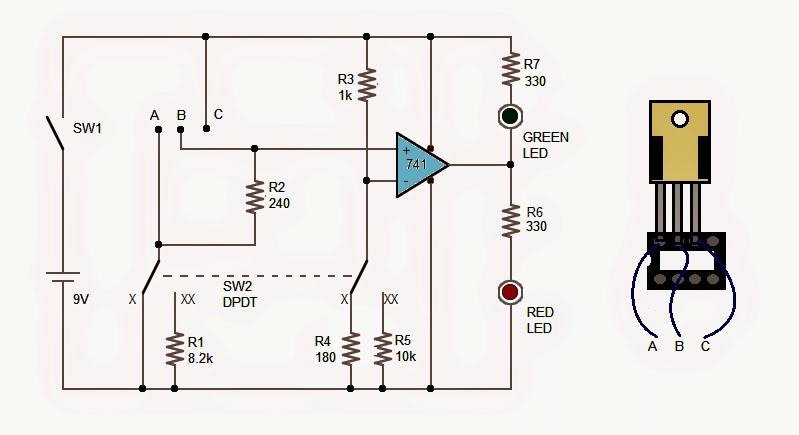

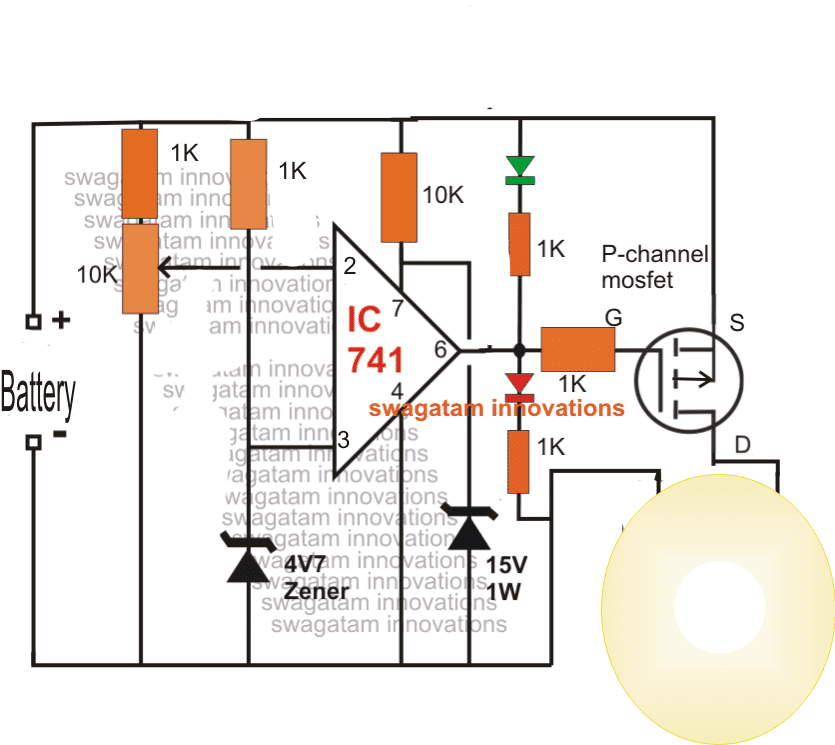

দ্য অর্ধ বিয়োগকার লজিক্যাল সার্কিট লজিক গেটগুলি ব্যবহার করে ব্যাখ্যা করা যেতে পারে:

- 1 এক্সওর গেট

- 1 গেট নয়

- 1 এবং গেট

উপস্থাপনা হয়

অর্ধ বিয়োগকার লজিক্যাল সার্কিট

অর্ধ-বিয়োগকার ব্লক ডায়াগ্রাম

অর্ধেক বিয়োগকারকের ব্লক চিত্রটি উপরে দেখানো হয়েছে। এটিতে দুটি ইনপুট প্রয়োজন পাশাপাশি দুটি আউটপুট দেয়। এখানে ইনপুটগুলি এএন্ডবি দ্বারা প্রতিনিধিত্ব করা হয়, এবং আউটপুটগুলি ডিফারেন্স এবং ধার করা হয়।

উপরের সার্কিটটি EX-OR & NAND গেট দিয়ে ডিজাইন করা যেতে পারে। এখানে, ন্যান্ড গেটটি এ্যান্ড এবং নট গেট ব্যবহার করে তৈরি করা যেতে পারে। সুতরাং আমাদের অর্ধেক সাবট্র্যাক্টর সার্কিট তৈরির জন্য তিনটি লজিক গেট প্রয়োজন যথা EX-OR গেট, নট গেট এবং ন্যান্ড গেট।

অ্যান্ড এবং নট গেটের সংমিশ্রণে ন্যানড গেট নামে একটি পৃথক সংযুক্ত গেট তৈরি হয়। প্রাক্তন-ওআর গেট আউটপুটটি ডিফারেন্স বিট এবং ন্যানড গেট আউটপুট একই ইনপুট এএন্ডবি এর জন্য ধার করা বিট হবে।

এবং গেট

এ্যান্ড-গেট এক ধরণের ডিজিটাল লজিক গেট যা একাধিক ইনপুট এবং একটি একক আউটপুট এবং ইনপুট সংমিশ্রণের উপর ভিত্তি করে এটি যৌক্তিক সংমিশ্রণ সম্পাদন করবে। এই গেটের সমস্ত ইনপুট যখন বেশি হবে, তখন আউটপুট বেশি হবে অন্যথায় আউটপুট কম হবে। সত্য টেবিল সহ অ্যান্ড গেটের লজিক ডায়াগ্রামটি নীচে দেখানো হয়েছে।

এবং গেট এবং সত্য ছক

গেট নেই

নট-গেটটি এক ধরণের ডিজিটাল লজিক গেট যা একক ইনপুট এবং ইনপুটের উপর ভিত্তি করে আউটপুট বিপরীত হবে। উদাহরণস্বরূপ, যখন নট গেটের ইনপুট বেশি হবে তখন আউটপুট কম হবে। সত্য টেবিল সহ নো-গেটের লজিক চিত্রটি নীচে দেখানো হয়েছে। এই ধরণের লজিক গেট ব্যবহার করে, আমরা NAND এবং NOR গেটগুলি কার্যকর করতে পারি।

গেট এবং সত্যের ছক নয়

প্রাক্তন-ওআর গেট

এক্সক্লুসিভ-ওআর বা এক্স-ওআর গেটটি হ'ল এক ধরণের ডিজিটাল লজিক গেট 2 ইনপুট এবং একক আউটপুট সহ। এই লজিক গেটের কাজটি ওআর গেটের উপর নির্ভর করে। এই গেটের যে কোনও ইনপুট যদি উচ্চ হয় তবে এক্স-ওআর গেটের আউটপুট বেশি হবে। EX-OR এর প্রতীক এবং সত্য সারণীটি নীচে দেখানো হয়েছে।

এক্সওর গেট এবং সত্য সারণী

নন্দ গেট ব্যবহার করে অর্ধ বিয়োগকারীর সার্কিট

সাবট্রাক্টর ডিজাইনিং এর মাধ্যমে করা যেতে পারে লজিক গেট ব্যবহার ন্যান্ড গেট এবং প্রাক্তন-ওআর গেটের মতো। এই অর্ধ বিয়োগকারীর সার্কিট ডিজাইন করার জন্য, আমাদের দুটি ধারণা যেমন পার্থক্য এবং orrowণ নিতে হবে তা জানতে হবে।

নন্দ গেট ব্যবহার করে অর্ধ বিয়োগকারীর সার্কিট

যদি আমরা সাবধানতার সাথে পর্যবেক্ষণ করি তবে এটি মোটামুটি স্পষ্ট যে এই সার্কিট দ্বারা কার্যকর করা বিভিন্ন অপারেশন যা সঠিকভাবে প্রাক্তন-ওআর গেট অপারেশনের সাথে সম্পর্কিত। অতএব, আমরা পার্থক্য তৈরির জন্য কেবল প্রাক্তন-OR গেটটি ব্যবহার করতে পারি। একইভাবে, অর্ধ সংযোজক সার্কিট দ্বারা উত্পাদিত ANDণটি অ্যান্ড- গেট এবং নট-গেটের মতো লজিক গেটগুলির মিশ্রণটি ব্যবহার করে সহজেই অর্জন করা যায়।

এই এইচএসটি NOR গেটগুলি ব্যবহার করে ডিজাইন করা যেতে পারে যেখানে এটির জন্য নির্মাণের জন্য 5 টি এনওআর গেট প্রয়োজন। NOR গেটগুলি ব্যবহার করে সার্কিট ডায়াগ্রাম অর্ধ বিয়োগকারক হিসাবে প্রদর্শিত হয়:

নর গেটস ব্যবহার করে অর্ধেক বিয়োগকারক

সঠিক তালিকা

প্রথম বিট | দ্বিতীয় বিট | পার্থক্য (প্রাক্তন-ও আউট) | ধার (ন্যান্ড আউট) |

0 | 0 | 0 | 0 |

| ঘ | 0 | ঘ | 0 |

0 | ঘ | ঘ | ঘ |

| ঘ | ঘ | 0 | 0 |

ভিএইচডিএল এবং টেস্টবেঞ্চ কোড

অর্ধেক বিয়োগকারকের জন্য ভিএইচডিএল কোডটি নীচে ব্যাখ্যা করা হয়েছে:

লাইব্রেরি আইইইই

IEEE.STD_LOGIC_1164.ALL ব্যবহার করুন

আইইইইএসটিএসডি_এলজিইসি_আরআইটিএইচ.এল.এল ব্যবহার করুন

আইইইইএসটিএসডি_এলজিআইসি_উএনজিআইএনডিএল ব্যবহার করুন use

সত্তা হাফ_সুব 1

বন্দর (একটি: STD_LOGIC এ)

খ: এসটিডি_লজিতে

এইচএস_ডিফ: এসটিডি_লজিক আউট

এইচএস_বোর: এসটিডি_লজিক আউট)

শেষ হাফ_সুব 1

হাফ_সুব 1 এর আর্কিটেকচার আচরণগত

শুরু

এইচএস_ডিফ<=a xor b

এইচএস_বরো<=(not a) and b

দ্য এইচএসের জন্য টেস্টবেঞ্চ কোড নীচে হিসাবে ব্যাখ্যা করা হয়:

লাইব্রেরি আইইইইই

Ieee.std_logic_1164.ALL ব্যবহার করুন

ENTITY HS_tb IS

শেষ এইচএস_টিবি

এইচএস_টিবি IS এর সংরক্ষণাগার HS_tb

কম্পোনেন্ট এইচএস

পোর্ট (ক: IN স্টাড_লোগিক)

বি: ইন স্টিড_লগিক

এইচএস_ডিফ: আউট স্টডি_লগিক

এইচএস_বোর: আউট স্ট্যান্ড_লগিক

)

সমাপ্তি কম্পন

সংকেত একটি: std_logic: = '0'

সিগন্যাল বি: std_logic: = '0'

সিগন্যাল এইচএস_ডিফ: std_logic

সিগন্যাল এইচএস_বোর: স্ট্যান্ড_লগিক

শুরু করুন

নতুন: এইচএস পোর্ট ম্যাপ (

a => ক,

b => খ,

এইচএস_ডিফ => এইচএস_ডিফ,

এইচএস_বরো => এইচএস_বরো

)

stim_proc: প্রক্রিয়া

শুরু

প্রতি<= ‘0’

খ<= ‘0’

30 এনএস জন্য অপেক্ষা করুন

প্রতি<= ‘0’

খ<= ‘1’

30 এনএস জন্য অপেক্ষা করুন

প্রতি<= ‘1’

খ<= ‘0’

30 এনএস জন্য অপেক্ষা করুন

প্রতি<= ‘1’

খ<= ‘1’

অপেক্ষা করুন

শেষ প্রক্রিয়া

শেষ

অর্ধ বিয়োগকার ব্যবহার করে সম্পূর্ণ বিয়োগকারক

একটি সম্পূর্ণ সাবট্রাক্টর একটি সম্মিলনীয় ডিভাইস যা দুটি বিট ব্যবহার করে বিয়োগের কার্যকারিতা পরিচালনা করে এবং এটি মেনইউন্ড এবং সাবট্রেন্ড হয়। সার্কিটটি ধারটিকে পূর্ববর্তী আউটপুট হিসাবে বিবেচনা করে এবং এতে দুটি আউটপুট সহ তিনটি ইনপুট রয়েছে। তিনটি ইনপুট হ'ল মিনিট, সাবট্রেন্ড এবং পূর্ববর্তী আউটপুট থেকে প্রাপ্ত ইনপুট যা ধার করা হয় এবং দুটি আউটপুট হ'ল পার্থক্য এবং orrowণ।

সম্পূর্ণ সাবট্রাক্টর লজিকাল ডায়াগ্রাম

জন্য সত্য টেবিল সম্পূর্ণ বিয়োগকারক হয়

| ইনপুটস | আউটপুটস | |||

| এক্স | ওয়াই | ইয়িন | এফএস_ডিফ | এফএস_বোর |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | ঘ | ঘ | ঘ |

| 0 | ঘ | 0 | ঘ | ঘ |

| 0 | ঘ | ঘ | 0 | ঘ |

| ঘ | 0 | 0 | ঘ | 0 |

| ঘ | 0 | ঘ | 0 | 0 |

| ঘ | ঘ | 0 | 0 | 0 |

| ঘ | ঘ | ঘ | ঘ | ঘ |

উপরের সত্যের সারণির সাহায্যে অর্ধ বিয়োগকারক ব্যবহার করে পূর্ণ বিয়োগকারীর প্রয়োগের জন্য লজিকাল ডায়াগ্রাম বিজ্ঞাপন সার্কিট চিত্রটি নীচে দেখানো হয়েছে:

এইচএস ব্যবহার করে সম্পূর্ণ বিয়োগকারক

অর্ধ বিয়োগকারীর সুবিধা এবং সীমাবদ্ধতা

অর্ধ বিয়োগকারীর সুবিধা:

- এই সার্কিটটির বাস্তবায়ন এবং নির্মাণ সহজ এবং সহজ

- এই সার্কিটটি ডিজিটাল সিগন্যাল প্রসেসিংয়ে সর্বনিম্ন শক্তি খরচ করে

- গণনামূলক কার্যকারিতা উন্নত গতির হারে সম্পাদন করা যেতে পারে

এই সংযুক্ত সার্কিটের সীমাবদ্ধতাগুলি হ'ল:

যদিও অনেকগুলি ক্রিয়াকলাপ এবং কার্যকারিতাগুলিতে অর্ধ বিয়োগকারীর বিস্তৃত প্রয়োগ রয়েছে, কিছু সীমাবদ্ধতা রয়েছে এবং সেগুলি হ'ল:

- অর্ধেক বিয়োগকারক সার্কিটগুলি পূর্ববর্তী আউটপুটগুলি থেকে যেখানে 'এই orrow সার্কিটের এটির চূড়ান্ত ব্যর্থতা' থেকে 'ধার' গ্রহণ করবে না

- অনেকগুলি রিয়েল-টাইম অ্যাপ্লিকেশন অসংখ্য বিট বিয়োগের বিয়োগকে কেন্দ্র করে, অর্ধ বিয়োগকারীর ডিভাইসগুলি অনেকগুলি বিট বিয়োগ করার কোনও ক্ষমতা রাখে না

অর্ধ বিয়োগীর আবেদন

অর্ধ বিয়োগকারীর প্রয়োগগুলির মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

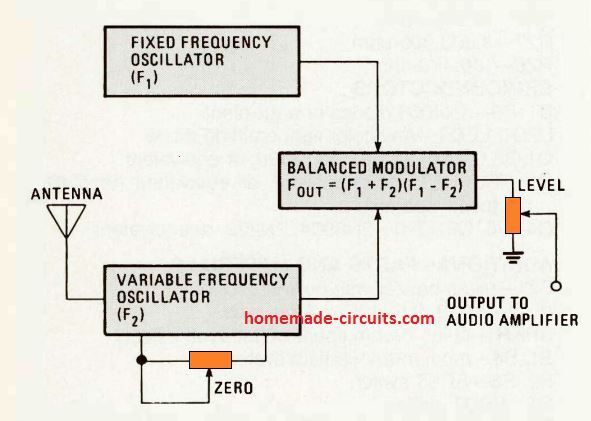

- অর্ধ বিয়োগকার অডিও বা রেডিও সংকেতের শক্তি হ্রাস করতে ব্যবহৃত হয়

- এটা হতে পারে পরিবর্ধক ব্যবহৃত শব্দ বিকৃতি কমাতে

- অর্ধ বিয়োগকারক প্রসেসরের ALU- এ ব্যবহৃত

- এটি অপারেটরগুলি বৃদ্ধি এবং হ্রাস করতে ব্যবহৃত হতে পারে এবং ঠিকানাগুলিও গণনা করে

- অর্ধ বিয়োগকারকে সর্বনিম্ন উল্লেখযোগ্য কলাম সংখ্যাগুলি বিয়োগ করতে ব্যবহৃত হয়। বহু-অঙ্কের সংখ্যার বিয়োগের জন্য, এটি এলএসবির জন্য ব্যবহার করা যেতে পারে।

সুতরাং, উপরের অর্ধেক বিয়োগকার তত্ত্ব থেকে, শেষ পর্যন্ত, আমরা এই সার্কিটটি ব্যবহার করে আমরা একটি বাইনারি বিট থেকে অন্য থেকে বিভাজন এবং orrowণের মতো আউটপুট সরবরাহ করতে পারি তা বন্ধ করতে পারি। একইভাবে, আমরা ন্যান্ড গেটস সার্কিটের পাশাপাশি NOR গেটগুলি ব্যবহার করে অর্ধেক বিয়োগকারকের নকশা করতে পারি। অন্যান্য ধারণাগুলি জানতে হবে সেগুলি কী অর্ধ বিয়োগকারীর ভেরিলোগ কোড এবং কীভাবে আরটিএল স্কিম্যাটিক চিত্রটি আঁকতে পারে?

![গ্লিটারিং এলইডি ফ্লাওয়ার সার্কিট [মাল্টিকালার এলইডি লাইট ইফেক্ট]](https://electronics.jf-parede.pt/img/3-phase-power/3B/glittering-led-flower-circuit-multicolored-led-light-effect-1.jpg)