এই পোস্টে আমরা শিখব কিভাবে আলাদা ট্রানজিস্টর ব্যবহার করে NOT, AND, NAND, OR, এবং NOR লজিক গেট তৈরি করা যায়। ট্রানজিস্টর লজিক গেট ব্যবহার করার প্রধান সুবিধা হল তারা 1.5 V এর কম ভোল্টেজেও কাজ করতে পারে।

কিছু ইলেকট্রনিক অ্যাপ্লিকেশনে উপলব্ধ ভোল্টেজ TTL বা এমনকি CMOS ICs পাওয়ার জন্য অপর্যাপ্ত হতে পারে। এটি বিশেষত ব্যাটারি চালিত গ্যাজেটগুলির জন্য সত্য। কোন সন্দেহ নেই, আপনার কাছে সর্বদা 3-ভোল্ট লজিক আইসি বিকল্প থাকে। যাইহোক, এগুলি সর্বদা উত্সাহী বা পরীক্ষকদের কাছে সহজে অ্যাক্সেসযোগ্য নয় এবং তারা তাদের সংজ্ঞায়িত ভোল্টেজ স্পেসিফিকেশনের নীচে কাজ করে না (সাধারণত 2.5 ভোল্ট ডিসির নীচে)।

উপরন্তু, একটি ব্যাটারি চালিত অ্যাপ্লিকেশনে শুধুমাত্র একটি 1.5-ভোল্ট ব্যাটারির জন্য জায়গা থাকতে পারে। আচ্ছা, তাহলে আপনি কি করতে যাচ্ছেন? সাধারণত আইসি লজিক গেটস ট্রানজিস্টরাইজড লজিক গেট দ্বারা প্রতিস্থাপিত হতে পারে। প্রতিটি নির্দিষ্ট লজিক গেটের জন্য, সাধারণত কয়েকটি ট্রানজিস্টরের প্রয়োজন হয় এবং একটি সাধারণ নট গেট ইনভার্টার লজিকের জন্য শুধুমাত্র একটি ট্রানজিস্টর প্রয়োজন।

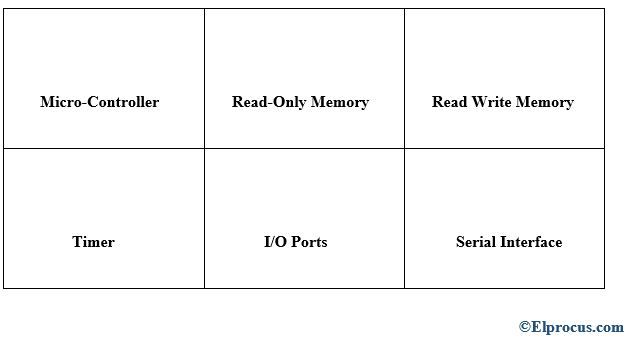

FETs বনাম বাইপোলার ট্রানজিস্টর

ফিল্ড ইফেক্ট ট্রানজিস্টর (এফইটি) বনাম বাইপোলার ট্রানজিস্টর : লো-ভোল্টেজ লজিক সার্কিটের জন্য কোনটি ভালো বিকল্প? একটি মহান বৈশিষ্ট্য তথ্য তাদের 'চালু' প্রতিরোধ অবিশ্বাস্যভাবে কম হয়. উপরন্তু, তাদের খুব কম গেট-টার্ন-অন কারেন্ট প্রয়োজন।

যাইহোক, অত্যন্ত কম-ভোল্টেজ অ্যাপ্লিকেশনগুলিতে তাদের একটি সীমাবদ্ধতা রয়েছে। সাধারণত, গেট ভোল্টেজের সীমা এক ভোল্ট বা তার বেশি। উপরন্তু, উপলব্ধ ভোল্টেজ FET-এর সর্বোত্তম কাজের পরিসরের নীচে হ্রাস পেতে পারে যদি একটি কারেন্ট-লিমিটিং বা পুল-ডাউন প্রতিরোধক গেটের সাথে সংযুক্ত থাকে।

বিপরীতভাবে, বাইপোলার সুইচিং ট্রানজিস্টরগুলির অত্যন্ত কম ভোল্টেজ, একক ব্যাটারি অ্যাপ্লিকেশনে একটি সুবিধা রয়েছে কারণ তাদের চালু করার জন্য শুধুমাত্র 0.6 থেকে 0.7 ভোল্টের প্রয়োজন হয়।

অধিকন্তু, বেশিরভাগ সাধারণ FET, যা সাধারণত আপনার নিকটস্থ ইলেকট্রনিক্স দোকানে বুদ্বুদ প্যাকে বিক্রি হয়, প্রায়শই বাইপোলার ট্রানজিস্টরের চেয়ে দামী হয়। এছাড়াও, বাইপোলার ট্রানজিস্টরের একটি বাল্ক প্যাকেট সাধারণত এক জোড়া FET-এর দামে কেনা যেতে পারে।

বাইপোলার ট্রানজিস্টর হ্যান্ডলিংয়ের চেয়ে FET হ্যান্ডলিং উল্লেখযোগ্যভাবে বেশি যত্নের প্রয়োজন। ইলেক্ট্রোস্ট্যাটিক এবং সাধারণ পরীক্ষামূলক অপব্যবহার FETগুলিকে বিশেষভাবে ক্ষতির ঝুঁকিপূর্ণ করে তোলে। পোড়া উপাদানগুলি পরীক্ষা বা উদ্ভাবনের একটি উপভোগ্য, সৃজনশীল সন্ধ্যা নষ্ট করতে পারে, ডিবাগিংয়ের মানসিক ব্যথা ভুলে যাওয়ার জন্য নয়।

ট্রানজিস্টর স্যুইচ করার মূল বিষয়

এই প্রবন্ধে ব্যাখ্যা করা লজিক সার্কিট উদাহরণগুলি বাইপোলার এনপিএন ট্রানজিস্টর ব্যবহার করে কারণ তারা সাশ্রয়ী মূল্যের এবং বিশেষ পরিচালনার প্রয়োজন নেই। ডিভাইস বা এটিকে সমর্থন করে এমন অংশগুলির ক্ষতি এড়াতে, আপনার সার্কিট সংযোগ করার আগে উপযুক্ত নিরাপত্তা ব্যবস্থা গ্রহণ করা উচিত।

যদিও আমাদের সার্কিটগুলি প্রধানত বাইপোলার জংশন ট্রানজিস্টর (BJTs) কেন্দ্রিক, তবে তারা FET প্রযুক্তি ব্যবহার করে সমানভাবে ভালভাবে তৈরি করা যেতে পারে।

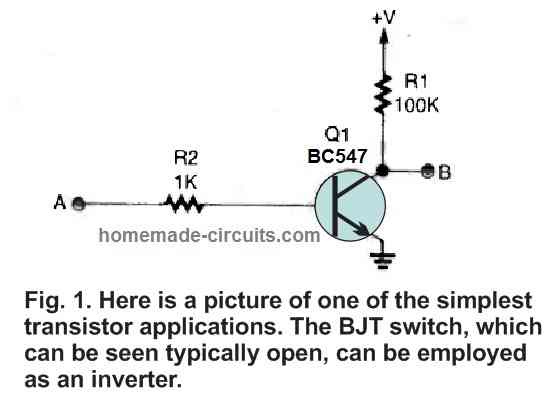

মৌলিক সুইচ সার্কিট একটি সহজ ট্রানজিস্টর অ্যাপ্লিকেশন, যা সবচেয়ে সহজ ডিজাইনগুলির মধ্যে একটি।

একটি একক ট্রানজিস্টর দিয়ে একটি নট গেট তৈরি করা

ট্রানজিস্টর সুইচের একটি পরিকল্পিত চিত্র 1-এ দেখানো হয়েছে। এটি একটি নির্দিষ্ট অ্যাপ্লিকেশনে কীভাবে প্রয়োগ করা হয় তার উপর নির্ভর করে, সুইচটিকে হয় কম রাখা বা সাধারণত খোলা হিসাবে দেখা যেতে পারে।

একটি সাধারণ নট গেট ইনভার্টার লজিক গেট চিত্র 1-এ দেখানো সোজা সুইচিং সার্কিট দ্বারা তৈরি করা যেতে পারে (যেখানে পয়েন্ট A হল ইনপুট)। একটি NOT গেট এমনভাবে কাজ করে যে যদি ট্রানজিস্টরের বেস (বিন্দু A; Q1) কোন DC বায়াস প্রদান না করা হয় তবে এটি বন্ধ থাকবে, ফলে আউটপুটে উচ্চ বা লজিক 1 (V+ স্তরের সমান) হবে ( বিন্দু বি)।

যাইহোক, ট্রানজিস্টর সক্রিয় হয় যখন সঠিক পক্ষপাত Q1 এর বেসে প্রদান করা হয়, সার্কিটের আউটপুট কম বা লজিক 0 (প্রায় শূন্য সম্ভাবনার সমান) ঠেলে দেয়। ট্রানজিস্টর, মনোনীত Q1, একটি সাধারণ-উদ্দেশ্য বাইপোলার ট্রানজিস্টর, বা একটি BC547, যা সাধারণত কম-পাওয়ার সুইচিং এবং অ্যামপ্লিফায়ার অ্যাপ্লিকেশনগুলিতে ব্যবহৃত হয়।

যেকোন ট্রানজিস্টর যা এর সমতুল্য (যেমন 2N2222, 2N4401, ইত্যাদি) কাজ করবে। কম বর্তমান ড্রেন এবং সামঞ্জস্যের মধ্যে একটি সমঝোতা করার জন্য R1 এবং R2 এর মানগুলি নির্বাচন করা হয়েছিল৷ সমস্ত ডিজাইনে, প্রতিরোধকগুলি হল 1/4 ওয়াট, 5% ইউনিট।

সরবরাহ ভোল্টেজ 1.4 এবং 6 ভোল্ট ডিসির মধ্যে সামঞ্জস্যযোগ্য। লক্ষ্য করুন যে লোড প্রতিরোধক এবং আউটপুট সংযোগ ট্রানজিস্টরের ইমিটারে স্থানান্তরিত হলে সার্কিটটি বাফারের মতো কাজ করতে পারে।

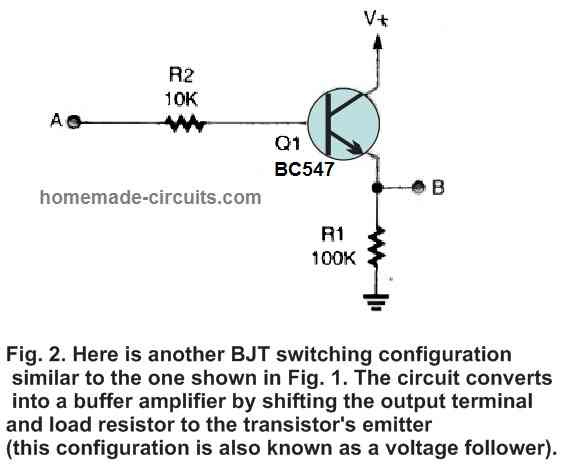

একটি একক BC547 BJT ব্যবহার করে একটি বাফার গেট তৈরি করা

একটি ভোল্টেজ ফলোয়ার, বা বাফার এমপ্লিফায়ার হল এক ধরনের লজিক সুইচিং কনফিগারেশন যা চিত্র 2-তে দেখানো হয়েছে। এটি উল্লেখ্য যে লোড প্রতিরোধক এবং আউটপুট টার্মিনাল এই সার্কিটে ট্রানজিস্টরের কালেক্টর থেকে এর ইমিটারে স্থানান্তরিত হয়েছে, যা এই নকশা এবং চিত্র 1-এ দেখানো একটির মধ্যে প্রাথমিক পার্থক্য।

লোড প্রতিরোধক এবং আউটপুট টার্মিনালকে BJT-এর অন্য প্রান্তে সরিয়ে নিয়ে ট্রানজিস্টরের কার্যকারিতাও 'ফ্লিপ' হতে পারে।

অন্য কথায়, যখন সার্কিটের ইনপুটে কোনো পক্ষপাত প্রদান করা হয় না, তখন সার্কিটের আউটপুট কম থাকে; যাইহোক, যখন সার্কিটের ইনপুটে পর্যাপ্ত ভোল্টেজ সরবরাহ করা হয়, তখন সার্কিটের আউটপুট উচ্চ হয়ে যায়। (এটি আগের সার্কিটে যা ঘটে তার ঠিক বিপরীত।)

ট্রানজিস্টর ব্যবহার করে টু-ইনপুট লজিক গেট ডিজাইন করা

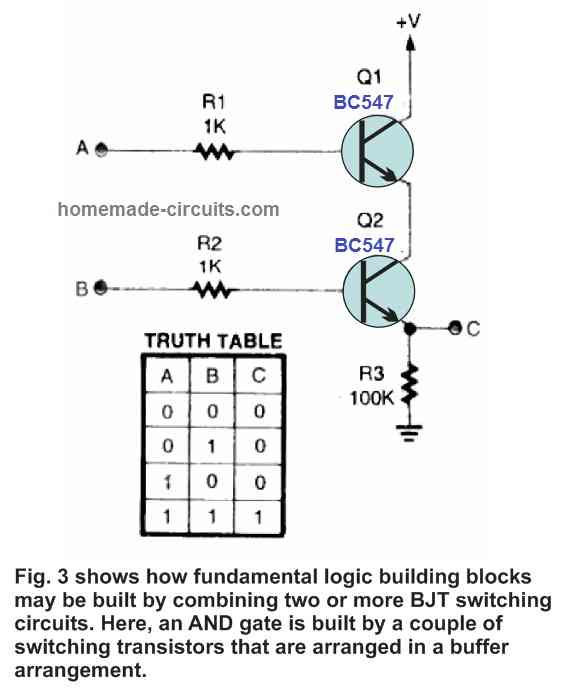

এবং দুটি ট্রানজিস্টর ব্যবহার করে গেট

চিত্র 3 ব্যাখ্যা করে কিভাবে একটি মৌলিক দুই-ইনপুট এবং গেট একটি জোড়া বাফার ব্যবহার করে তৈরি করা যেতে পারে, সেই গেটের জন্য সত্য সারণী সহ। সত্য সারণী প্রতিটি স্বতন্ত্র সেট ইনপুটের জন্য আউটপুট ফলাফল কী হবে তা ব্যাখ্যা করে। পয়েন্ট A এবং B সার্কিটের ইনপুট হিসাবে ব্যবহৃত হয়, এবং পয়েন্ট C সার্কিটের আউটপুট হিসাবে কাজ করে।

সত্য সারণী থেকে এটি লক্ষ্য করা গুরুত্বপূর্ণ যে ইনপুট প্যারামিটারের মাত্র একটি সেট একটি লজিক-উচ্চ আউটপুট সংকেত দেয়, যেখানে অন্যান্য সমস্ত ইনপুট সংমিশ্রণের ফলে একটি লজিক-লো আউটপুট হয়। চিত্র 3-এ AND গেটের আউটপুট V+ এর সামান্য নিচে থাকে একবার এটি উচ্চ হয়ে গেলে।

দুটি ট্রানজিস্টরের (Q1 এবং Q2) মধ্যে ভোল্টেজ ড্রপের কারণে এটি ঘটে।

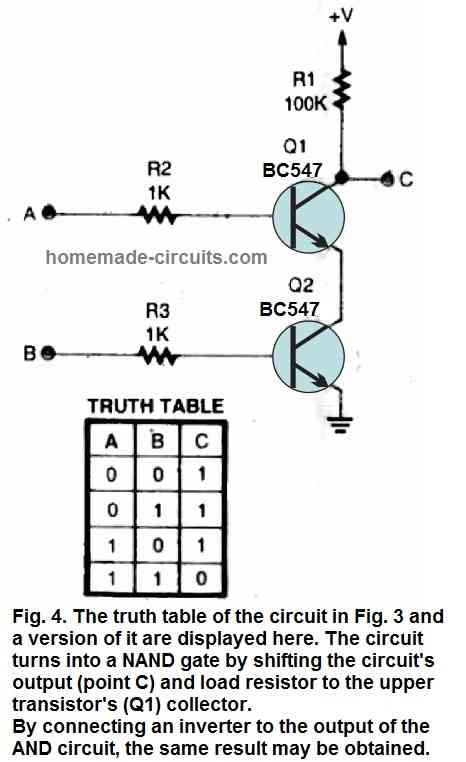

দুটি ট্রানজিস্টর ব্যবহার করে NAND গেট

চিত্র 3-এ সার্কিটের আরেকটি বৈকল্পিক এবং সংশ্লিষ্ট সত্য সারণী চিত্র 4-এ দেখানো হয়েছে। আউটপুট (বিন্দু C) এবং আউটপুট রোধকে উপরের ট্রানজিস্টরের (Q1) সংগ্রাহকে স্থানান্তর করে সার্কিটটি একটি NAND গেটে পরিণত হয়।

যেহেতু Q1 এবং Q2 উভয়ই R1-এর নিম্ন দিকটিকে মাটিতে টেনে আনতে সুইচ করতে হবে, তাই আউটপুট C-এ ভোল্টেজের ক্ষতি খুবই নগণ্য।

যদি ট্রানজিস্টর AND বা ট্রানজিস্টর NAND গেটগুলির দুটির বেশি ইনপুটের প্রয়োজন হয়, তাহলে আরও ট্রানজিস্টর দেখানো ডিজাইনে তিনটি, চার, ইত্যাদি ইনপুট AND বা NAND গেট দেওয়ার জন্য ভালভাবে সংযুক্ত হতে পারে৷

যাইহোক, স্বতন্ত্র ট্রানজিস্টরের ভোল্টেজের ক্ষতিপূরণের জন্য, V+ অনুরূপভাবে বৃদ্ধি করা উচিত।

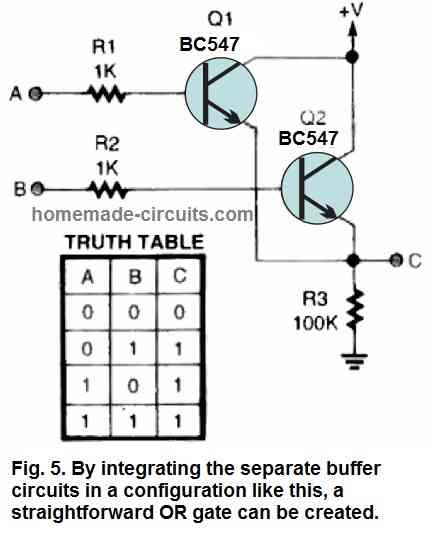

বা দুটি ট্রানজিস্টর ব্যবহার করে গেট

দুটি ইনপুট সহ লজিক সার্কিটের আরেকটি রূপ চিত্র 5-এ OR-গেট সার্কিটের সত্য টেবিলের সাথে দেখা যেতে পারে।

ইনপুট A বা ইনপুট B উচ্চ ধাক্কা দিলে সার্কিটের আউটপুট বেশি হয়, তবে ক্যাসকেডেড ট্রানজিস্টরের কারণে, ভোল্টেজ ড্রপ 0.5 ভোল্টের বেশি হয়। তবুও, প্রদর্শিত পরিসংখ্যানগুলি নির্দেশ করে যে পরবর্তী ট্রানজিস্টর গেটটি পরিচালনা করার জন্য যথেষ্ট ভোল্টেজ এবং কারেন্ট রয়েছে।

দুটি ট্রানজিস্টর ব্যবহার করে NOR গেট

চিত্র 6 আমাদের তালিকার পরবর্তী গেটটিকে চিত্রিত করে, একটি দুই-ইনপুট নওর গেট, এর সত্যতা টেবিলের সাথে। কিভাবে AND এবং NAND গেট একে অপরের সাথে সাড়া দেয়, OR এবং NOR সার্কিট একই কাজ করে।

প্রদর্শিত গেটগুলির প্রতিটি কমপক্ষে এক বা একাধিক সংলগ্ন ট্রানজিস্টর গেটগুলি সক্রিয় করার জন্য যথেষ্ট ড্রাইভ সরবরাহ করতে সক্ষম।

ট্রানজিস্টর লজিক গেট অ্যাপ্লিকেশন

উপরের ব্যাখ্যা করা ডিজিটাল সার্কিটগুলি দিয়ে আপনি কী করবেন যা এখন আপনার আছে? আপনি প্রচলিত TTL বা CMOS গেট দিয়ে যা কিছু করতে পারেন, কিন্তু সরবরাহ ভোল্টেজের সীমাবদ্ধতা নিয়ে চিন্তা না করে। এখানে ট্রানজিস্টর-লজিক গেটের কয়েকটি প্রয়োগ রয়েছে।

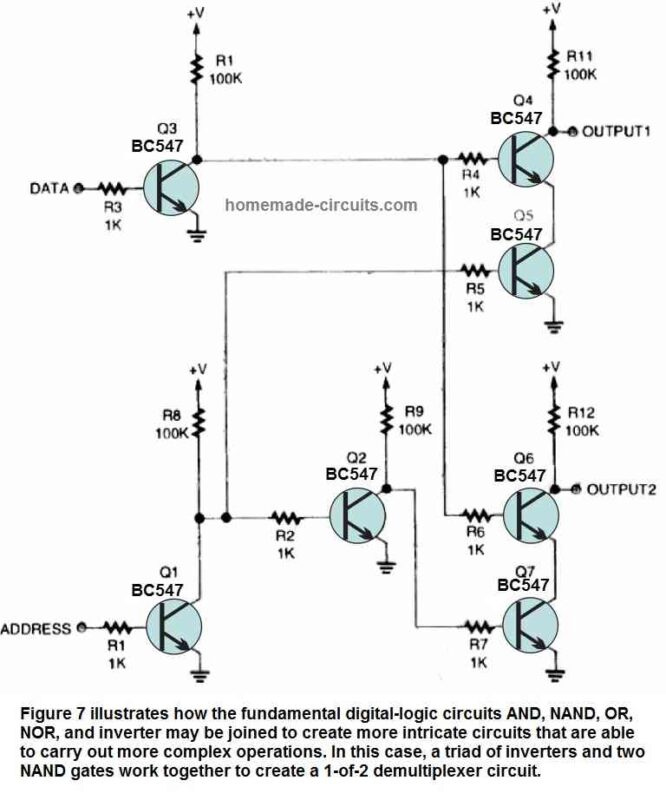

ডেমল্টিপ্লেক্সার সার্কিট

তিনটি নট গেট এবং দুটি NAND সার্কিট সহ একটি 1-এর-2 ডিমাল্টিপ্লেক্সার চিত্র 7-এ দেখা গেছে। উপযুক্ত আউটপুটটি ওয়ান-বিট 'অ্যাড্রেস ইনপুট' ব্যবহার করে বেছে নেওয়া হয়েছে, যা OUTPUT1 বা OUTPUT2 হতে পারে, যখন ড্রাইভিং তথ্য প্রয়োগ করা হয়। ডেটা ইনপুট ব্যবহার করে সার্কিটে।

সার্কিটটি সবচেয়ে কার্যকরভাবে কাজ করে যখন ডেটা রেট 10 kHz-এর নিচে বজায় থাকে। সার্কিটের কার্যকারিতা সহজবোধ্য। ডেটা ইনপুটটি প্রয়োজনীয় সংকেত সহ সরবরাহ করা হয়, যা Q3 চালু করে এবং Q3 এর সংগ্রাহকের আগত ডেটাকে উল্টে দেয়।

ADDRESS ইনপুট কম হলে Q1-এর আউটপুট বেশি চালিত হয় (গ্রাউন্ডেড বা কোনও সংকেত দেওয়া হয় না)। Q1 এর সংগ্রাহক এ, উচ্চ আউটপুট দুটি পাথে বিভক্ত। প্রথম পথে, Q1-এর আউটপুট Q5-এর বেসে সরবরাহ করা হয় (একটি দুই-ইনপুট NAND গেটের পাগুলির মধ্যে একটি), এটি চালু করে এবং তাই Q4 এবং Q5 দিয়ে গঠিত NAND গেটটিকে 'সক্রিয়' করে।

দ্বিতীয় পথে, Q1 এর উচ্চ আউটপুট একই সাথে অন্য NOT গেটের (Q2) ইনপুটে সরবরাহ করা হয়। একটি ডবল ইনভার্সশনের মধ্য দিয়ে যাওয়ার পরে, Q2 এর আউটপুট কম হয়ে যায়। এই নিম্নটি Q7 এর বেস সরবরাহ করা হয় (একটি দ্বিতীয় NAND গেটের একটি টার্মিনাল, Q6 এবং Q7 দ্বারা গঠিত), এইভাবে NAND সার্কিটটি বন্ধ করে দেয়।

ডেটা ইনপুটে প্রয়োগ করা যেকোন তথ্য বা সংকেত এই পরিস্থিতিতে OUTPUT1 এ পৌঁছায়। বিকল্পভাবে, যদি ADDRESS ইনপুটে একটি উচ্চ সংকেত দেওয়া হয় তবে পরিস্থিতি বিপরীত হয়। অর্থ, সার্কিটে প্রদত্ত যেকোন তথ্য OUTPUT2 এ দেখাবে যেহেতু Q4/Q5 NAND গেট নিষ্ক্রিয় করা হয়েছে এবং Q6/Q7 NAND গেট সক্রিয় করা হয়েছে।

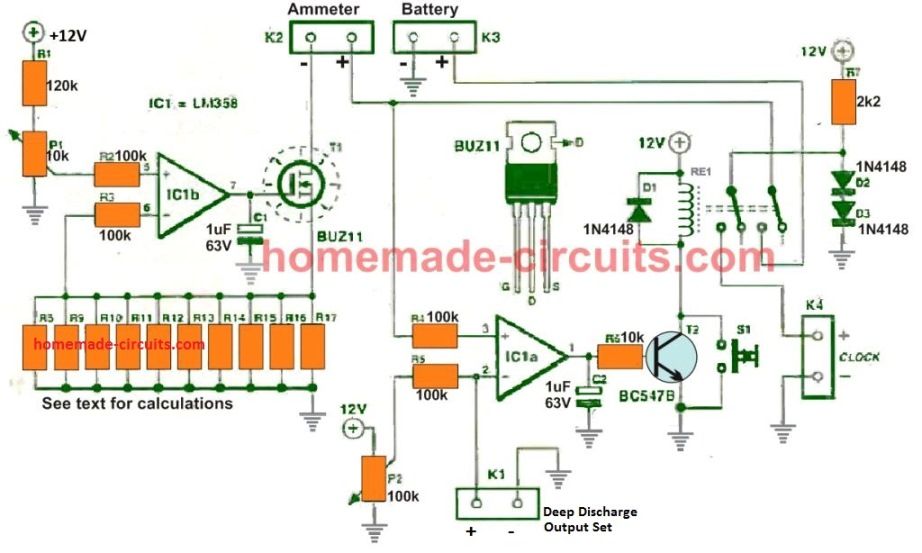

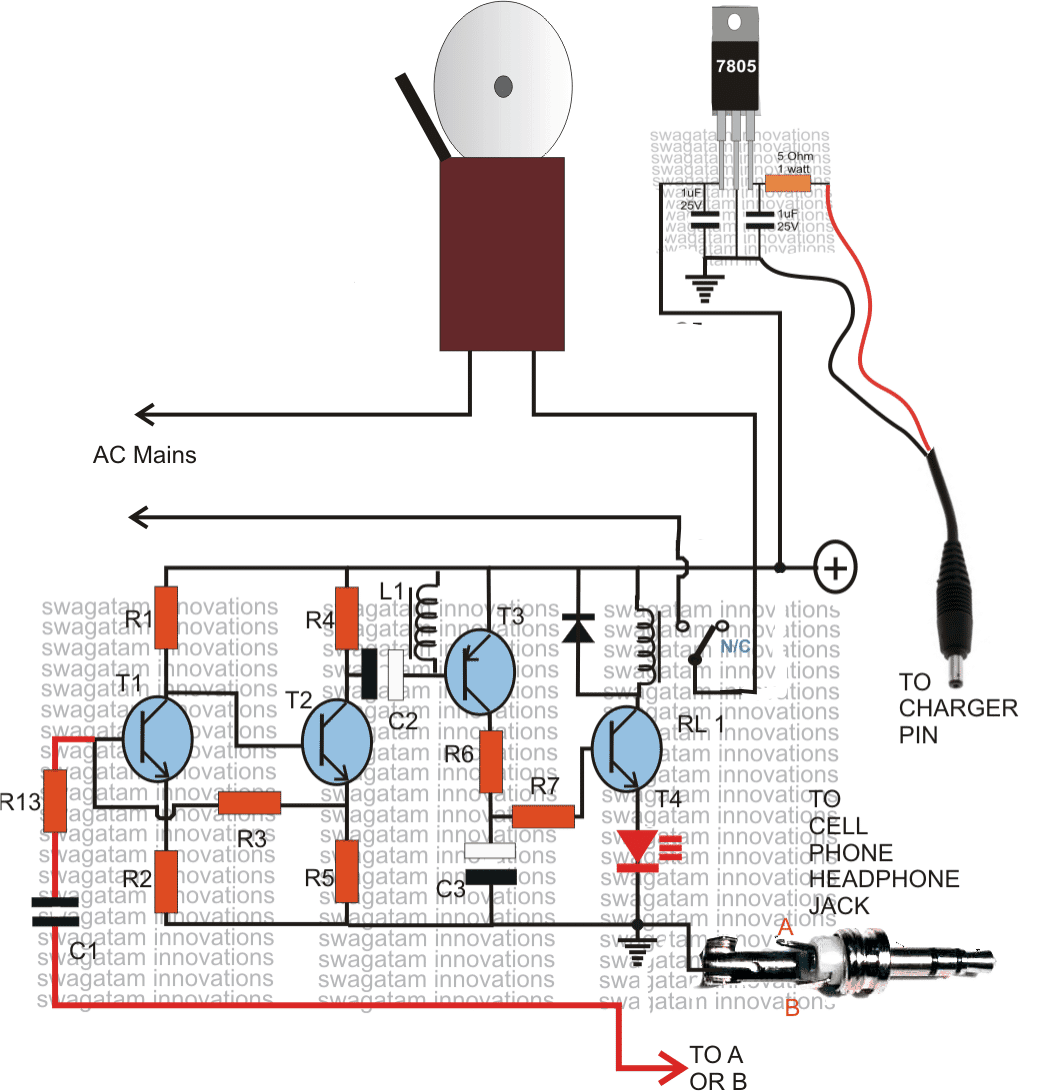

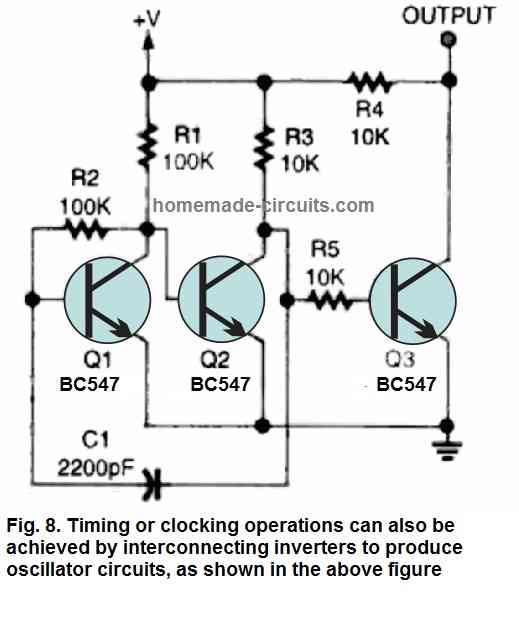

অসিলেটর সার্কিট (ক্লক জেনারেটর)

আমাদের পরবর্তী ট্রানজিস্টর লজিক গেট অ্যাপ্লিকেশন, চিত্র 8-এ চিত্রিত, একটি বেসিক ক্লক জেনারেটর (একটি অসিলেটর নামেও পরিচিত) যা তিনটি সাধারণ নট গেট ইনভার্টার দিয়ে তৈরি (যার মধ্যে একটি ফিডব্যাক প্রতিরোধক, R2 ব্যবহার করে পক্ষপাতদুষ্ট, যা এটিকে ভিতরে রাখে অ্যানালগ অঞ্চল)।

আউটপুট বর্গাকার করার জন্য, একটি তৃতীয় নট গেট (Q3) যা অসিলেটর আউটপুটে পরিপূরক প্রদান করে। সার্কিটের অপারেটিং ফ্রিকোয়েন্সি পরিবর্তন করতে C1 মান বৃদ্ধি বা হ্রাস করা যেতে পারে। আউটপুট তরঙ্গরূপের কম্পোনেন্ট প্রায় 7 kHz এর সাথে V+ 1.5 ভোল্ট ডিসিতে, নির্দেশিত উপাদান মান ব্যবহার করে।

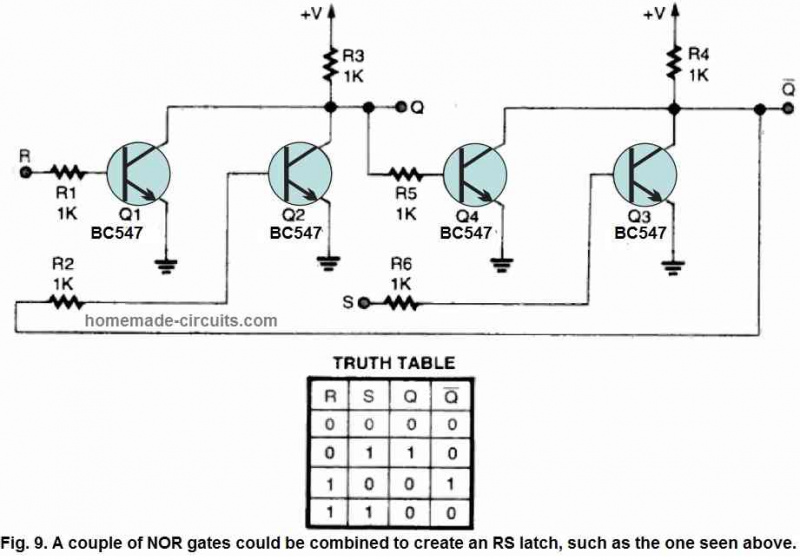

আরএস ল্যাচ সার্কিট

চিত্র 9 আমাদের চূড়ান্ত অ্যাপ্লিকেশন সার্কিট দেখায়, দুটি NOR গেট দ্বারা গঠিত একটি RS ল্যাচ। Q এবং Q আউটপুটে একটি সুস্থ আউটপুট ড্রাইভ নিশ্চিত করার জন্য, প্রতিরোধক R3 এবং R4 1k ohms এ সামঞ্জস্য করা হয়।

আরএস ল্যাচের সত্য টেবিলটি পরিকল্পিত নকশার পাশাপাশি প্রদর্শিত হয়। এগুলি হল কয়েকটি বিশ্বস্ত, লো-ভোল্টেজ, ডিজিটাল, লজিক-গেট সার্কিটের কয়েকটি চিত্র যা পৃথক ট্রানজিস্টর ব্যবহার করে তৈরি করা যেতে পারে।

ট্রানজিস্টরাইজড লজিক ব্যবহার করে সার্কিটের অনেকগুলো অংশের প্রয়োজন

এই সমস্ত লো-ভোল্টেজ ট্রানজিস্টরাইজড লজিক সার্কিট ব্যবহার করে অনেক সমস্যার সমাধান করা যেতে পারে। যাইহোক, এই ট্রানজিস্টরাইজড গেটগুলির মধ্যে অনেকগুলি নিয়োগ করা নতুন সমস্যার দিকে নিয়ে যেতে পারে।

ট্রানজিস্টরাইজ এবং প্রতিরোধকের সংখ্যা মোটামুটি বিশাল হতে পারে যদি আপনি যে অ্যাপ্লিকেশনটি তৈরি করছেন তাতে প্রচুর পরিমাণে গেট থাকে, মূল্যবান স্থান দখল করে।

পৃথক ইউনিটের জায়গায় ট্রানজিস্টর অ্যারে (অনেক ট্রানজিস্টর প্লাস্টিকের মধ্যে ঘেরা) এবং এসআইপি (সিঙ্গেল ইনলাইন প্যাকেজ) প্রতিরোধক ব্যবহার করা এই সমস্যা সমাধানের একটি উপায়।

উপরের পদ্ধতিটি একটি পিসিবিতে তাদের পূর্ণ আকারের সমতুল্যগুলির সমান পারফরম্যান্স বজায় রেখে এক টন স্থান বাঁচাতে পারে। ট্রানজিস্টর অ্যারে সারফেস-মাউন্ট, 14-পিন থ্রু-হোল এবং কোয়াড প্যাক প্যাকেজিং-এ দেওয়া হয়।

বেশিরভাগ সার্কিটের জন্য, ট্রানজিস্টরের ধরনের মিশ্রণ বেশ গ্রহণযোগ্য হতে পারে।

তবুও, এটি পরামর্শ দেওয়া হয় যে পরীক্ষাকারী ট্রানজিস্টরাইজড লজিক সার্কিটগুলি তৈরি করার জন্য একক ধরণের ট্রানজিস্টরের সাথে কাজ করে (অর্থাৎ আপনি যদি BC547 ব্যবহার করে একটি গেটের একটি অংশ তৈরি করেন, তারপর অন্য অবশিষ্ট গেটগুলিও তৈরি করার জন্য একই BJT ব্যবহার করার চেষ্টা করুন)।

যুক্তি হল যে বিভিন্ন ট্রানজিস্টর ভেরিয়েন্টের কিছুটা ভিন্ন বৈশিষ্ট্য থাকতে পারে এবং এইভাবে ভিন্নভাবে আচরণ করতে পারে।

উদাহরণস্বরূপ, কিছু ট্রানজিস্টরের জন্য বেস সুইচ-অন সীমা অন্যটির চেয়ে বড় বা ছোট হতে পারে, অথবা একটি সামগ্রিক বর্তমান লাভ হতে পারে যা একটু বেশি বা কম।

অন্যদিকে, এক ধরনের ট্রানজিস্টরের বাল্ক বক্স কেনার খরচও কম হতে পারে। যদি আপনার লজিক গেটগুলি ম্যাচিং ট্রানজিস্টরগুলি ব্যবহার করে তৈরি করা হয় তবে আপনার সার্কিটগুলির কার্যকারিতা বৃদ্ধি পাবে এবং সম্পূর্ণভাবে প্রকল্পটি শেষ পর্যন্ত আরও ফলপ্রসূ হবে৷