JTAG (জয়েন্ট টেস্ট অ্যাকশন গ্রুপ) হল একটি সুপ্রতিষ্ঠিত IEEE 1149.1 স্ট্যান্ডার্ড যা ইলেকট্রনিক বোর্ডের মধ্যে ঘটে যাওয়া ম্যানুফ্যাকচারিং সমস্যা সমাধানের জন্য 1980 সালে তৈরি করা হয়েছিল। মুদ্রিত সার্কিট বোর্ড . এই প্রযুক্তিটি প্রতিটি জটিল বোর্ডের জন্য পর্যাপ্ত পরীক্ষার অ্যাক্সেস প্রদান করতে ব্যবহৃত হয় যখন পরীক্ষার অ্যাক্সেস কমছিল। এইভাবে, সীমানা স্ক্যান প্রযুক্তি চালু করা হয়েছিল এবং JTAG মান বা JTAG স্পেসিফিকেশন প্রতিষ্ঠিত. ইলেকট্রনিক্সের জটিলতা দিন দিন বৃদ্ধি পাচ্ছে, তাই JTAG স্পেসিফিকেশন জটিল এবং কমপ্যাক্ট ইলেকট্রনিক্স ইউনিট পরীক্ষা করার জন্য স্বীকৃত পরীক্ষার ফর্ম্যাটে পরিণত হয়েছে। এই নিবন্ধটি একটি ওভারভিউ আলোচনা JTAG প্রোটোকল - অ্যাপ্লিকেশনগুলির সাথে কাজ করা।

JTAG কি?

IEEE 1149.1 স্ট্যান্ডার্ড টেস্ট এক্সেস পোর্টের পাশাপাশি বাউন্ডারি-স্ক্যান আর্কিটেকচারকে যে নাম দেওয়া হয় তা JTAG (জয়েন্ট টেস্ট অ্যাকশন গ্রুপ) নামে পরিচিত। এই সীমানা স্ক্যান আর্কিটেকচার বেশিরভাগ কম্পিউটারের মধ্যে ব্যবহৃত হয় প্রসেসর কারণ JTAG সহ প্রথম প্রসেসর Intel প্রকাশ করেছিল। এই IEEE স্ট্যান্ডার্ডটি সহজভাবে সংজ্ঞায়িত করে যে কীভাবে একটি কম্পিউটারের সার্কিট্রি পরীক্ষা করা হয় তা নিশ্চিত করার জন্য যে এটি উত্পাদন পদ্ধতির পরে সঠিকভাবে কাজ করছে কিনা। সার্কিট বোর্ডগুলিতে, সোল্ডার জয়েন্টগুলি পরীক্ষা করার জন্য পরীক্ষা করা হয়।

জয়েন্ট টেস্ট অ্যাকশন গ্রুপ প্রতিটি IC প্যাডের সাথে পরীক্ষকদের জন্য একটি পিন-আউট ভিউ প্রদান করে যা সার্কিট বোর্ডের মধ্যে কোনো ত্রুটি সনাক্ত করতে সাহায্য করে। একবার এই প্রোটোকলটি একটি চিপের সাথে ইন্টারফেস করা হলে, এটি একটি বিকাশকারীকে চিপটিকে নিয়ন্ত্রণ করার পাশাপাশি অন্যান্য চিপের সাথে এর সংযোগগুলিকে অনুমতি দিয়ে চিপের সাথে একটি প্রোব সংযুক্ত করতে পারে। জয়েন্ট টেস্ট অ্যাকশন গ্রুপের ইন্টারফেসটি ডেভেলপাররা একটি ইলেকট্রনিক ডিভাইসে ফার্মওয়্যারকে অ-উদ্বায়ী মেমরিতে অনুলিপি করার জন্য ব্যবহার করতে পারে।

কনফিগারেশন/পিন আউট

জয়েন্ট টেস্ট অ্যাকশন গ্রুপে 20-পিন রয়েছে যেখানে প্রতিটি পিন এবং এর কার্যকারিতা নীচে আলোচনা করা হয়েছে।

Pin1 (VTref): এটি টার্গেট রেফারেন্স ভোল্টেজ পিন যা টার্গেটের প্রধান পাওয়ার সাপ্লাইয়ের সাথে সংযোগ করতে ব্যবহৃত হয় যা 1.5 থেকে 5.0VDC পর্যন্ত।

Pin2 (Vsupply): এটি লক্ষ্য সরবরাহ ভোল্টেজ যা লক্ষ্য 1.5VDC - 5.0VDC এর প্রধান ভোল্টেজ সরবরাহ সংযোগ করতে ব্যবহৃত হয়।

Pin3 (nTRST): এটি একটি টেস্ট রিসেট পিন যা ট্যাপ কন্ট্রোলারের স্টেট মেশিন রিসেট করতে ব্যবহৃত হয়।

পিন (4, 6, 8, 10, 12, 14, 16, 18 এবং 20): এগুলি সাধারণ GND পিন।

Pin5 (TDI): এটি পিনে টেস্ট ডেটা। এই তথ্য টার্গেট ডিভাইসে স্থানান্তরিত হয়. এই পিনটি টার্গেট বোর্ডে একটি সংজ্ঞায়িত অবস্থায় টানতে হবে।

Pin7 (TMS): এটি টেস্ট মোড স্টেট পিন যা ট্যাপ কন্ট্রোলারের স্টেট মেশিনের পরবর্তী অবস্থা নির্ধারণ করতে টানা হয়।

Pin9 (TCK): এটি একটি টেস্ট ক্লক পিন যা TAP কন্ট্রোলারে অভ্যন্তরীণ স্টেট মেশিন অপারেশনগুলিকে সিঙ্ক্রোনাইজ করে।

Pin11 (RTCK): এটি হল ইনপুট রিটার্ন TCK পিন যা অভিযোজিত ক্লকিং সমর্থন করে এমন ডিভাইসগুলিতে ব্যবহৃত হয়।

Pin13 (TDO): এটি টেস্ট ডেটা আউট পিন, তাই ডেটা টার্গেট ডিভাইস থেকে ফ্লাইসওয়াটারে সরানো হয়।

Pin15 (nSRST): এটি টার্গেট সিস্টেম রিসেট পিন যা টার্গেটের প্রধান রিসেট সিগন্যালের সাথে সংযুক্ত।

পিন 17 এবং 19 (NC): এগুলি সংযুক্ত পিন নয়।

JTAG কাজ করছে

JTAG এর আসল ব্যবহার সীমানা পরীক্ষার জন্য। এখানে, সিপিইউ এবং এর মতো দুটি আইসি সহ একটি সাধারণ মুদ্রিত সার্কিট বোর্ড রয়েছে FPGA . একটি সাধারণ বোর্ডে অনেক আইসি অন্তর্ভুক্ত থাকতে পারে। সাধারণভাবে, আইসি-তে অনেকগুলি পিন অন্তর্ভুক্ত থাকে যা অনেকগুলি সংযোগের সাথে যৌথভাবে সংযুক্ত থাকে। এখানে, নিম্নলিখিত চিত্রে, শুধুমাত্র চারটি সংযোগ দেখানো হয়েছে।

তাই আপনি যদি অনেক বোর্ড ডিজাইন করেন যেখানে প্রতিটি বোর্ডে হাজার হাজার সংযোগ থাকে। তার মধ্যে কিছু খারাপ বোর্ড আছে। তাই কোন বোর্ড কাজ করছে আর কোনটা কাজ করছে না তা আমাদের যাচাই করতে হবে। সে জন্য জয়েন্ট টেস্ট অ্যাকশন গ্রুপ তৈরি করা হয়েছে।

এই প্রোটোকলটি সমস্ত চিপের কন্ট্রোল পিন ব্যবহার করতে পারে তবে নিম্নলিখিত চিত্রে, জয়েন্ট টেস্ট অ্যাকশন গ্রুপ CPU-এর সমস্ত আউটপুট পিন এবং FPGA-এর সমস্ত ইনপুট পিন তৈরি করতে চলেছে৷ এর পরে, CPU-এর পিনগুলি থেকে কিছু পরিমাণ ডেটা প্রেরণ করে এবং FPGA থেকে পিনের মানগুলি পড়ে, JTAG বলে যে PCB বোর্ডের সংযোগগুলি ঠিক আছে।

প্রকৃতপক্ষে, জয়েন্ট টেস্ট অ্যাকশন গ্রুপে চারটি লজিক সিগন্যাল TDI, TDO, TMS এবং TCK অন্তর্ভুক্ত রয়েছে। এবং এই সংকেতগুলি একটি নির্দিষ্ট উপায়ে সংযুক্ত করা প্রয়োজন। প্রথমে, TMS এবং TCK JTAG-এর সমস্ত IC-এর সাথে সমান্তরালভাবে সংযুক্ত থাকে।

এর পরে, একটি চেইন গঠনের জন্য TDI এবং TDO উভয়ই সংযুক্ত। আপনি লক্ষ্য করতে পারেন, প্রতিটি JTAG অনুগত IC-তে 4- পিন থাকে যা JTAG-এর জন্য ব্যবহৃত হয় যেখানে 3-পিন ইনপুট এবং 4র্থ পিন হল আউটপুট। TRST এর মত পঞ্চম পিন ঐচ্ছিক। সাধারণত, JTAG পিনগুলি অন্য উদ্দেশ্যে শেয়ার করা হয় না।

জয়েন্ট টেস্ট অ্যাকশন গ্রুপ ব্যবহার করে, সমস্ত আইসি সীমানা পরীক্ষা ব্যবহার করে যার মূল কারণটি JTAG দ্বারা তৈরি করা হয়েছে। বর্তমানে, FPGAs কনফিগার করার মতো বিভিন্ন জিনিসের অনুমতি দেওয়ার জন্য এই প্রোটোকলের ব্যবহার বাড়ানো হয়েছে এবং এর পরে JTAG ডিবাগ করার উদ্দেশ্যে FPGA কোরে ব্যবহার করা হয়।

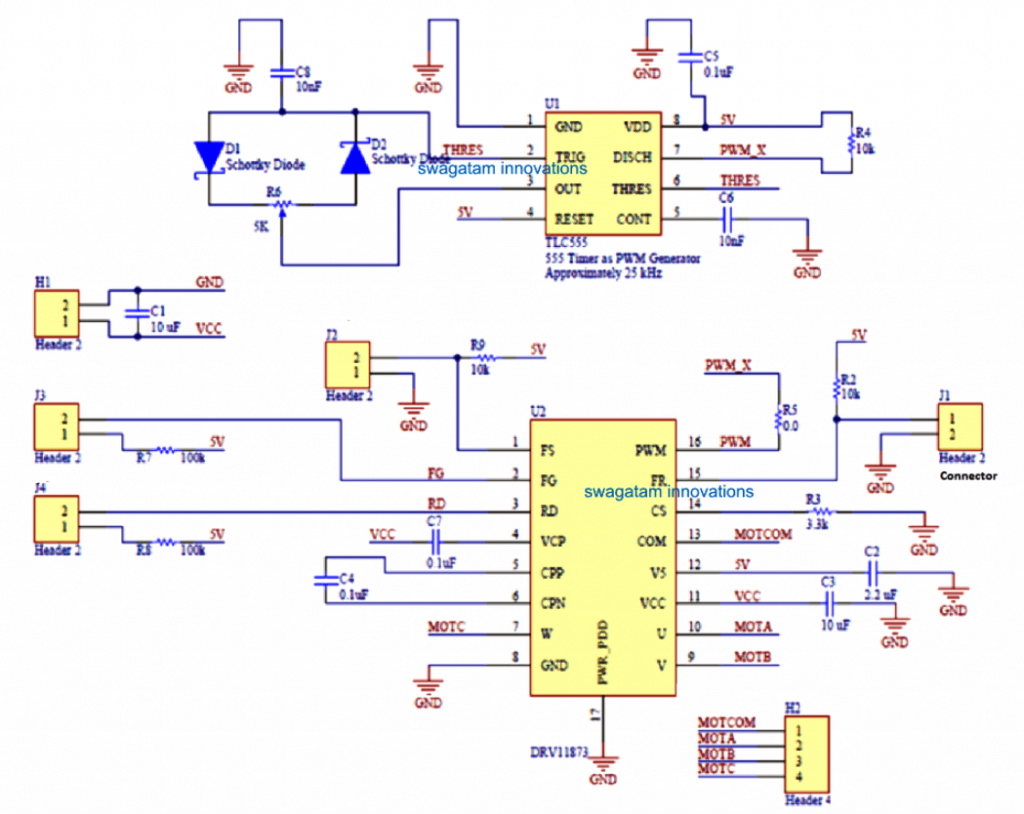

JTAG আর্কিটেকচার

JTAG আর্কিটেকচার নীচে দেখানো হয়েছে। এই আর্কিটেকচারে, ডিভাইসের মূল লজিক এবং পিনগুলির মধ্যে সমস্ত সংকেতগুলি বিএসআর বা বাউন্ডারি স্ক্যান রেজিস্টার নামক একটি সিরিয়াল স্ক্যান পাথের মাধ্যমে বাধাপ্রাপ্ত হয়। এই BSR-এর মধ্যে বিভিন্ন বাউন্ডারি স্ক্যান 'সেল' অন্তর্ভুক্ত রয়েছে। সাধারণত, এই বাউন্ডারি স্ক্যান সেলগুলি দৃশ্যমান হয় না তবে এগুলি ডিভাইস পিন থেকে টেস্ট মোডের মধ্যে মান সেট করতে বা পড়তে ব্যবহার করা যেতে পারে।

TCK, TMS, TDI, TDO, এবং TRST-এর মতো সীমানা স্ক্যান অপারেশনকে সমর্থন করার জন্য TAP বা টেস্ট অ্যাক্সেস পোর্ট নামে পরিচিত JTAG ইন্টারফেসটি বিভিন্ন সংকেত ব্যবহার করে।

- TCK বা টেস্ট ক্লক সিগন্যাল কেবল একটি রাষ্ট্রীয় মেশিনের অভ্যন্তরীণ ক্রিয়াকলাপগুলিকে সিঙ্ক্রোনাইজ করে।

- TMS বা টেস্ট মোড সিলেক্ট সিগন্যাল পরবর্তী অবস্থা নির্ধারণের জন্য একটি টেস্ট ক্লক সিগন্যালের ক্রমবর্ধমান প্রান্তে নমুনা করা হয়।

- TDI বা টেস্ট ডেটা ইন সিগন্যাল পরীক্ষা ডিভাইসে স্থানান্তরিত ডেটাকে নির্দেশ করে অন্যথায় প্রোগ্রামিং লজিক। ভিতরের স্টেট মেশিনটি সঠিক অবস্থায় থাকলে তা TCK এর ক্রমবর্ধমান প্রান্তে নমুনা করা হয়।

- টিডিও বা টেস্ট ডেটা আউট সিগন্যাল অন্যথায় প্রোগ্রামিং লজিক পরীক্ষা ডিভাইসের স্থানান্তরিত ডেটাকে নির্দেশ করে। অভ্যন্তরীণ স্টেট মেশিনটি সঠিক অবস্থায় থাকলে তা TCK-এর ক্রমহ্রাসমান প্রান্তে বৈধ

- TRST বা টেস্ট রিসেট হল একটি ঐচ্ছিক পিন যা TAP কন্ট্রোলারের স্টেট মেশিন রিসেট করতে ব্যবহৃত হয়।

ট্যাপ কন্ট্রোলার

JTAG এর আর্কিটেকচারে টেস্ট অ্যাক্সেস পয়েন্টটি একটি TAP কন্ট্রোলার, একটি নির্দেশনা রেজিস্টার এবং টেস্ট ডেটা রেজিস্টার দ্বারা গঠিত। এই কন্ট্রোলারে টেস্টিং স্টেট মেশিন রয়েছে যা TMS এবং TCK সিগন্যাল পড়ার জন্য দায়ী। এখানে, ডেটা i/p পিনটি সহজভাবে IC কোর এবং ফিজিক্যাল পিনের মধ্যে থাকা বাউন্ডারি সেলগুলিতে ডেটা লোড করতে এবং ডেটা রেজিস্টারগুলির একটিতে বা নির্দেশনা রেজিস্টারে ডেটা লোড করতে ব্যবহৃত হয়। ডেটা o/p পিন রেজিস্টার বা বাউন্ডারি সেল থেকে ডেটা পড়ার জন্য ব্যবহৃত হয়।

টিএপি কন্ট্রোলারের স্টেট মেশিন টিএমএস দ্বারা নিয়ন্ত্রিত হয় এবং এটি টিসিকে দ্বারা ক্লক করা হয়। স্টেট মেশিন নির্দেশ মোড এবং ডেটা মোডের মতো দুটি ভিন্ন মোড বোঝাতে দুটি পথ ব্যবহার করে।

নিবন্ধন করে

বাউন্ডারি স্ক্যানের মধ্যে দুই ধরনের রেজিস্টার পাওয়া যায়। প্রতিটি কমপ্লায়েন্ট ডিভাইসে কমপক্ষে দুই বা তার বেশি ডেটা রেজিস্টার এবং একটি নির্দেশনা রেজিস্টার অন্তর্ভুক্ত থাকে।

নির্দেশনা রেজিস্টার

নির্দেশনা রেজিস্টার বর্তমান নির্দেশ ধরে রাখতে ব্যবহার করা হয়। তাই এর ডেটা TAP কন্ট্রোলার দ্বারা প্রাপ্ত সংকেতগুলির সাথে কী চালানো হবে তা নির্ধারণ করতে ব্যবহার করা হয়। প্রায়শই, নির্দেশনা রেজিস্টার ডেটা বর্ণনা করে যে কোন ডেটা রেজিস্টার সংকেতগুলিকে পাস করতে হবে।

ডেটা রেজিস্টার

ডেটা রেজিস্টার তিন ধরনের BSR (সীমানা স্ক্যান রেজিস্টার), বাইপাস এবং আইডি কোড রেজিস্টারে পাওয়া যায়। এবং এছাড়াও, অন্যান্য ডেটা রেজিস্টার থাকতে পারে, তবে JTAG স্ট্যান্ডার্ডের একটি উপাদান হিসাবে সেগুলি প্রয়োজনীয় নয়।

বাউন্ডারি স্ক্যান রেজিস্টার (বিএসআর)

BSR হল প্রধান টেস্টিং ডেটা রেজিস্টার যা ডিভাইস I/O পিন থেকে ডেটা স্থানান্তর করতে ব্যবহৃত হয়।

বাইপাস

বাইপাস হল একটি একক-বিট রেজিস্টার যা TDI – TDO থেকে ডেটা পাস করতে ব্যবহৃত হয়। সুতরাং এটি সার্কিটের মধ্যে থাকা অতিরিক্ত ডিভাইসগুলিকে সর্বনিম্ন ওভারহেড দ্বারা পরীক্ষা করার অনুমতি দেয়।

আইডি কোড

এই ধরনের ডেটা রেজিস্টারে আইডি কোডের পাশাপাশি ডিভাইসের রিভিশন নম্বর অন্তর্ভুক্ত থাকে। তাই এই ডেটা ডিভাইসটিকে তার BSDL (সীমানা স্ক্যান বর্ণনা ভাষা) ফাইলের সাথে সংযুক্ত করার অনুমতি দেয়। এই ফাইলটিতে ডিভাইসের জন্য সীমানা স্ক্যান কনফিগারেশন বিশদ অন্তর্ভুক্ত রয়েছে।

JTAG-এর কাজ হল, প্রাথমিকভাবে, নির্দেশ মোডটি বেছে নেওয়া হয় যেখানে এই মোড 'পাথ'-এর একটি স্টেট টিডিআই-এর নির্দেশের মধ্যে অপারেটরকে ঘড়ি দিতে দেয়। এর পরে।, রাষ্ট্রীয় যন্ত্রটি পুনর্বিন্যাস না হওয়া পর্যন্ত বিকাশ করে। বেশিরভাগ নির্দেশের জন্য পরবর্তী ধাপ হল ডেটা মোড নির্বাচন করা। তাই এই মোডে, ডেটা টিডিও থেকে পড়ার জন্য TDI এর মাধ্যমে লোড করা হয়। টিডিআই এবং টিডিও-র জন্য, ডেটা পাথগুলি ক্লক করা নির্দেশের সাথে সম্মতিতে সাজানো হবে। একবার রিড/রাইট অপারেশন সম্পন্ন হলে, আবার স্টেট মেশিন রিসেট অবস্থায় বিকশিত হবে।

JTAG বনাম UART এর মধ্যে পার্থক্য

JTAG এবং UART এর মধ্যে পার্থক্য নিম্নলিখিত অন্তর্ভুক্ত।

| JTAG |

UART |

| 'JTAG' শব্দের অর্থ হল জয়েন্ট টেস্ট অ্যাকশন গ্রুপ। | শব্দটি ' UART ” মানে ইউনিভার্সাল অ্যাসিঙ্ক্রোনাস রিসিভার/ট্রান্সমিটার। |

| এটি একটি সিঙ্ক্রোনাস ইন্টারফেস যা ফ্ল্যাশ প্রোগ্রাম করার জন্য অন্তর্নির্মিত হার্ডওয়্যার ব্যবহার করে . | UART একটি অ্যাসিঙ্ক্রোনাস ইন্টারফেস যা মেমরির মধ্যে চলে এমন একটি বুটলোডার ব্যবহার করে। |

| এটি পরীক্ষা পোর্টের একটি সেট যা ডিবাগিংয়ের জন্য ব্যবহৃত হয় তবে ফার্মওয়্যার প্রোগ্রাম করতেও ব্যবহার করা যেতে পারে (যা সাধারণত করা হয়)।

|

UART হল এক ধরণের চিপ যা একটি ডিভাইসে এবং থেকে যোগাযোগ নিয়ন্ত্রণ করে, যেমন একটি মাইক্রোকন্ট্রোলার, ROM, RAM ইত্যাদি। বেশিরভাগ সময়, এটি একটি সিরিয়াল সংযোগ যা আমাদের একটি ডিভাইসের সাথে যোগাযোগ করতে দেয়। |

| এগুলি চার ধরনের TDI, TDO, TCK, TMS এবং TRST পাওয়া যায়। | এই দুটি ধরনের বোবা UART এবং FIFO UART পাওয়া যায়. |

| জয়েন্ট টেস্ট অ্যাকশন গ্রুপ হল সিরিয়াল প্রোগ্রামিং বা ডেটা অ্যাক্সেস প্রোটোকল যা মাইক্রোকন্ট্রোলার এবং সম্পর্কিত ডিভাইসগুলির ইন্টারফেসিংয়ে ব্যবহৃত হয়। | একটি UART হল এক ধরণের চিপ অন্যথায় মাইক্রোকন্ট্রোলারের সাব-কম্পোনেন্ট যা RS-232/RS-485 এর মত একটি অ্যাসিঙ্ক্রোনাস সিরিয়াল স্ট্রীম তৈরি করার জন্য হার্ডওয়্যার প্রদান করতে ব্যবহৃত হয়। |

| JTAG উপাদানগুলি হল প্রসেসর, FPGA, CPLDs , ইত্যাদি | UART উপাদান হল CLK জেনারেটর, I/O শিফট রেজিস্টার, বাফার ট্রান্সমিট বা রিসিভ, সিস্টেম ডাটা বাস বাফার, কন্ট্রোল লজিক পড়া বা লেখা ইত্যাদি। |

JTAG প্রোটোকল বিশ্লেষক

JTAG প্রোটোকল বিশ্লেষক যেমন PGY-JTAG-EX-PD হল এক ধরণের প্রোটোকল বিশ্লেষক যার মধ্যে কিছু বৈশিষ্ট্য রয়েছে যা পরীক্ষার অধীনে হোস্ট এবং ডিজাইনের মধ্যে যোগাযোগ ক্যাপচার এবং ডিবাগ করার জন্য। এই ধরনের বিশ্লেষক হল অগ্রণী যন্ত্র যা পরীক্ষা ও ডিজাইন ইঞ্জিনিয়ারদের JTAG ট্র্যাফিক জেনারেট করার জন্য মাস্টার বা স্লেভের মতো PGY-JTAG-EX-PD সাজানোর মাধ্যমে এবং এর ডিকোড প্যাকেটগুলিকে ডিকোড করার মাধ্যমে JTAG-এর নির্দিষ্ট নকশাগুলি পরীক্ষা করার অনুমতি দেয়। জয়েন্ট টেস্ট অ্যাকশন গ্রুপ প্রোটোকল।

বৈশিষ্ট্য

JTAG প্রোটোকল বিশ্লেষকের বৈশিষ্ট্যগুলির মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

- এটি JTAG ফ্রিকোয়েন্সির 25MH পর্যন্ত সমর্থন করে।

- এটি একই সাথে বাসের জন্য JTAG ট্রাফিক এবং প্রোটোকল ডিকোড তৈরি করে।

- এটির JTAG মাস্টার ক্ষমতা আছে।

- পরিবর্তনশীল JTAG ডেটা গতি এবং শুল্ক চক্র।

- ব্যবহারকারী-সংজ্ঞায়িত TDI এবং TCK বিলম্ব।

- হোস্ট কম্পিউটার USB 2.0 বা 3.0 ইন্টারফেস।

- প্রোটোকল ডিকোডের মধ্যে ত্রুটি বিশ্লেষণ

- প্রোটোকল ডিকোডেড বাস টাইমিং ডায়াগ্রাম।

- একটি বড় বাফার প্রদানের জন্য হোস্ট কম্পিউটারে ক্রমাগত প্রোটোকল ডেটা স্ট্রিমিং।

- প্রোটোকল কার্যকলাপ তালিকা.

- বিভিন্ন গতিতে, একাধিক ডেটা ফ্রেম তৈরির সমন্বয়ের জন্য একটি ব্যায়াম স্ক্রিপ্ট লেখা যেতে পারে।

টাইমিং ডায়াগ্রাম

দ্য JTAG এর টাইমিং ডায়াগ্রাম প্রোটোকল নীচে দেখানো হয়েছে। নিম্নলিখিত চিত্রে, টিডিও পিনটি একটি শিফট-আইআর/শিফ্ট-ডিআর কন্ট্রোলার স্টেট ব্যতীত উচ্চ প্রতিবন্ধক অবস্থার মধ্যে থাকে।

Shift-IR এবং Shift-DR কন্ট্রোলার কন্ডিশনে, TDO পিন টার্গেটের মাধ্যমে TCK-এর ক্রমবর্ধমান প্রান্তে আপডেট করা হয় এবং হোস্টের মাধ্যমে TCK-এর ক্রমবর্ধমান প্রান্তে নমুনা করা হয়।

TDI এবং TMS উভয় পিনই টার্গেটের মাধ্যমে TCK এর ক্রমবর্ধমান প্রান্তে নমুনা করা হয়। ক্রমবর্ধমান প্রান্তে আপডেট করা হয়েছে অন্যথায় হোস্টের মাধ্যমে TCK।

অ্যাপ্লিকেশন

দ্য JTAG অ্যাপ্লিকেশন নিম্নলিখিত অন্তর্ভুক্ত.

- জয়েন্ট টেস্ট অ্যাকশন গ্রুপ প্রায়শই তাদের এমুলেশন বা ডিবাগ ফাংশনগুলিতে প্রবেশের অধিকার প্রদানের জন্য প্রসেসরগুলিতে ব্যবহৃত হয়।

- সমস্ত CPLDs এবং FPGA তাদের প্রোগ্রামিং ফাংশন অ্যাক্সেস দিতে একটি ইন্টারফেস হিসাবে এটি ব্যবহার করে।

- এটি শারীরিক অ্যাক্সেস ছাড়াই PCB পরীক্ষার জন্য ব্যবহৃত হয়

- এটি বোর্ড-স্তরের উত্পাদন পরীক্ষার জন্য ব্যবহৃত হয়।

এইভাবে, এই সব সম্পর্কে JTAG এর একটি ওভারভিউ - পিন কনফিগারেশন, অ্যাপ্লিকেশনগুলির সাথে কাজ করা। ইন্ডাস্ট্রি স্ট্যান্ডার্ড JTAG তৈরির পরে ডিজাইন যাচাইকরণের পাশাপাশি PCB পরীক্ষার জন্য ব্যবহৃত হয়। এখানে আপনার জন্য একটি প্রশ্ন, JTAG মানে?